-

-

-

Design Resources

- Design & Development

- Featured Design Tools

- Partners

- Content & Training

-

Support

-

Support Forums

Get help from our expert Renesas technical staff and community.

- Technical Support

- Training & Events

- Quality & Packaging

-

Support Forums

-

Sample & Buy

-

Buy Direct from Renesas

Customers can now choose the convenience of buying direct from Renesas.

- Ordering Resources

-

Buy Direct from Renesas

841484I

circleObsoleteFemtoClock® Crystal-to-0.7V Differential

Overview

Description

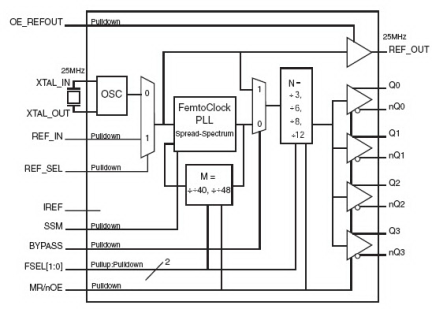

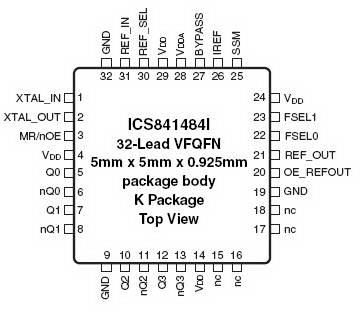

The 841484I is an optimized PCIe and sRIO clock generator. The device uses a 25MHz parallel resonant crystal to generate 100MHz, 125MHz, 200MHz and 400MHz clock signals, replacing solutions requiring multiple oscillator and fanout buffer solutions. The device has excellent phase jitter suitable to clock components requiring precise and low jitter PCIe, sRIO or both clock signals. The device also supports a configurable spread-spectrum generation for PCIe applications. Designed for telecom, networking and industrial applications, the 841484I can also drive the high-speed sRIO and PCIe SerDes clock inputs of communications processors, DSPs, switches and bridges.

Features

- Four 0.7V differential HCSL outputs: configurable for PCIe (100MHz or 200MHz) and sRIO (125MHz) clock signals

- One LVCMOS/LVTTL reference clock output

- Selectable crystal oscillator interface, 25MHz, 18pF parallel resonant crystal or LVCMOS/LVTTL single-ended reference clock input

- Supports the following output frequencies: 100MHz, 125MHz, 200MHz or 400MHz

- VCO frequency range: 950MHz - 1.25GHz

- Configurable spread-spectrum generation for PCIe

- PLL bypass and output enable

- RMS phase jitter @ 200MHz, using a 25MHz crystal (12kHz - 20MHz): 1.21ps (typical)

- PCI Express (2.5 Gb/S), Gen 2 (5 Gb/s) and Gen 3 (8 Gb/s) jitter compliant (REF_OUT disabled)

- Full 3.3V operating supply

- -40°C to 85°C ambient operating temperature

- Available in lead-free (RoHS 6) packages

Comparison

Applications

Documentation

|

|

|

|

|---|---|---|

| Type | Title | Date |

| Datasheet | PDF 914 KB | |

| Overview | PDF 2.40 MB | |

| End Of Life Notice | PDF 606 KB | |

| End Of Life Notice | PDF 599 KB | |

| Product Change Notice | PDF 596 KB | |

| Product Change Notice | PDF 544 KB | |

6 items

|

||

Design & Development

Models

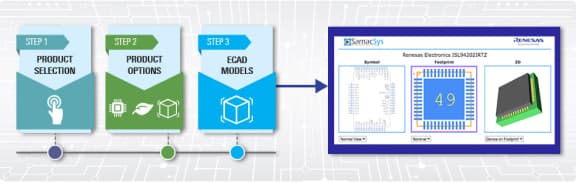

ECAD Models

Schematic symbols, PCB footprints, and 3D CAD models from SamacSys can be found by clicking on products in the Product Options table. If a symbol or model isn't available, it can be requested directly from the website.

Product Options

Pkg. Type |

Lead Count (#) |

Temp. Grade |

Pb (Lead) Free |

Carrier Type |

Buy / Sample |

|

|---|---|---|---|---|---|---|

| Part Number | ||||||

| VFQFPN | 32 | I | Yes | Tray | ||

| VFQFPN | 32 | I | Yes | Reel |

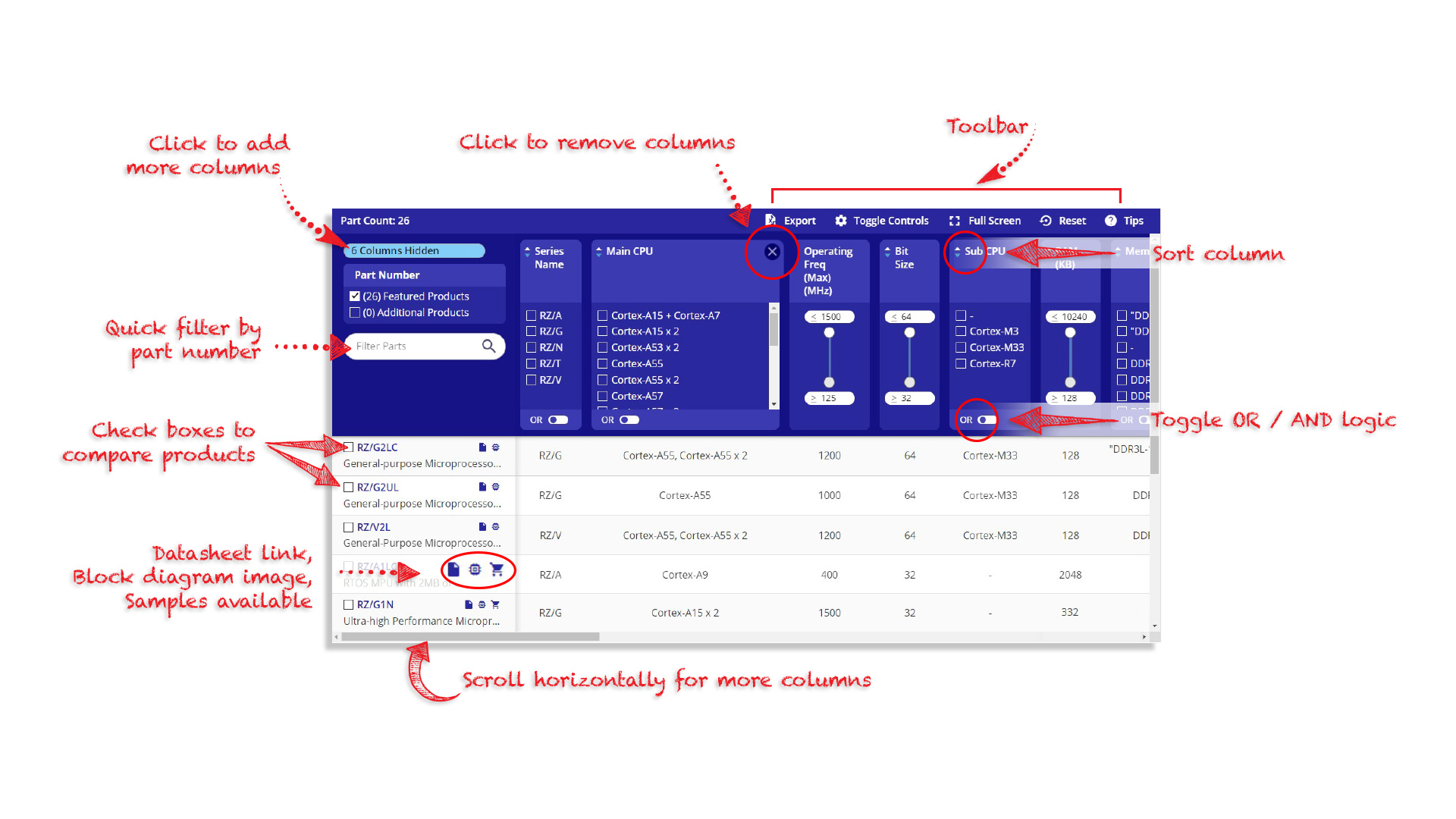

Tips for Using This Parametric Table:

- Hide Filters button in header: Collapse or expands filters

- Column sort buttons in header: Sort Column alphabetically / numerically descending or ascending

- Reset button in header: Reset all filters to the page default

- Full Screen button in header: Expand the table to full screen view (user must close out of full screen before they can interact with rest of page)

- Export button in header: Export the filtered results of the table to an Excel document

- Filter parts search bar in header: Type to filter table results by part number

- Hide column button in column headers: Select to hide columns in table

- AND / OR toggle switches in header: Toggles the logic of this particular filter to be “AND” or “OR” logic for filtering results

- Multiselect checkboxes at beginning of each row in table: Select these checkboxes to compare products against each other

- Document icon next to product name in row: View the featured document for this product

- Chip icon next to the right of the document icon in row: View the block diagram for this product

- Cart icon to the right of the chip icon: Indicates that samples are available for this product