# **High Performance Communication Buffer**

### **General Description**

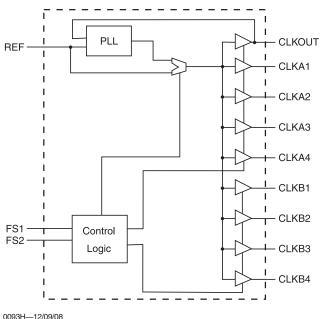

The **ICS91309** is a high performance, low skew, low jitter zero delay buffer. It uses a phase lock loop (PLL) technology to align, in both phase and frequency, the REF input with the CLKOUT signal. It is designed to distribute high speed clocks in communication systems operating at speeds from 10 to 133 MHz.

The **ICS91309** provides synchronization between the input and output. The synchronization is established via CLKOUT feed back to the input of the PLL. Since the skew between the input and output is less than +/- 350 pS, the part acts as a zero delay buffer.

**ICS91309** has two banks of four outputs controlled by two address lines. Depending on the selected address line, bank B or both banks can be put in a tri-state mode. In this mode, the PLL is still running and only the output buffers are put in a high impedance mode. The test mode shuts off the PLL and connects the input directly to the output buffers (see table below for functionality).

**ICS91309** comes in a 16-pin 150 mil SOIC, SSOP or 4.40mm TSSOP package. In the absence of REF input, the device will enter a powerdown mode. In this mode, the PLL is turned off and the output buffers are pulled low. Power down mode provides the lowest power consumption for a standby condition.

### **Block Diagram**

#### Features

- Zero input output delay

- Frequency range 10 133 MHz (3.3V)

- 5V tolerant input REF

- High loop filter bandwidth ideal for Spread Spectrum applications.

- Less than 125 ps cycle to cycle Jitter

- Skew controlled outputs

- Available in 16 pin, 150 mil SSOP, SOIC & 4.40mm TSSOP packages

- Skew: Group-to-Group: <215 ps</li>

- Skew within Group: <100 ps

- Commercial temperature range: 0°C to +70°C

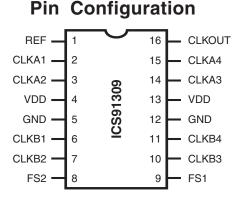

### 16 pin SSOP, SOIC & TSSOP

#### Functionality

| FS2 | FS1 | CLKA(1:4)             | CLKB(1:4)          | CLKOUT                | Ouput<br>Source | PLL<br>Shutdown |

|-----|-----|-----------------------|--------------------|-----------------------|-----------------|-----------------|

| 0   | 0   | Tristate              | Tristate           | Driven                | PLL             | N               |

| 0   | 1   | Driven                | Tristate           | Driven                | PLL             | N               |

| 1   | 0   | PLL<br>Bypass<br>Mode | PLL Bypass<br>Mode | PLL<br>Bypass<br>Mode | REF             | Y               |

| 1   | 1   | Driven                | Driven             | Driven                | PLL             | N               |

<sup>© 2019</sup> Renesas Electronics Corporation

# **Pin Descriptions**

| PIN # | PIN NAME            | PIN TYPE | DESCRIPTION                                  |

|-------|---------------------|----------|----------------------------------------------|

| 1     | REF <sup>1</sup>    | IN       | Input reference frequency, 5V tolerant input |

| 2     | CLKA1 <sup>2</sup>  | OUT      | Buffered clock output, Bank A                |

| 3     | CLKA2 <sup>2</sup>  | OUT      | Buffered clock output, Bank A                |

| 4, 13 | VDD                 | PWR      | Power Supply                                 |

| 5, 12 | GND                 | PWR      | Ground                                       |

| 6     | CLKB1 <sup>2</sup>  | OUT      | Buffered clock output, Bank B                |

| 7     | CLKB2 <sup>2</sup>  | OUT      | Buffered clock output, Bank B                |

| 8     | FS2 <sup>3</sup>    | IN       | Function select input, bit 2                 |

| 9     | FS1 <sup>3</sup>    | IN       | Function select input, bit 1                 |

| 10    | CLKB3 <sup>2</sup>  | OUT      | Buffered clock output, Bank B                |

| 11    | CLKB4 <sup>2</sup>  | OUT      | Buffered clock output, Bank B                |

| 14    | CLKA3 <sup>2</sup>  | OUT      | Buffered clock output, Bank A                |

| 15    | CLKA4 <sup>2</sup>  | OUT      | Buffered clock output, Bank A                |

| 16    | CLKOUT <sup>2</sup> | OUT      | Buffered clock output, internal feedback     |

Notes:

1. Weak pull-down

2. Weak pull-down on all outputs

3. Weak pull-ups on these inputs

### **Absolute Maximum Ratings**

| Supply Voltage                | 7.0 V                                 |

|-------------------------------|---------------------------------------|

| Logic Inputs (Except REF)     | GND –0.5 V to V <sub>DD</sub> + 0.5 V |

| Logic Input REF               | GND -0.5 V to GND + 5.5 V             |

| Ambient Operating Temperature | 0°C to +70°C                          |

| Storage Temperature           | –65°C to +150°C                       |

Stresses above those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These ratings are stress specifications only and functional operation of the device at these or any other conditions above those listed in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect product reliability.

#### **Electrical Characteristics - Input & Supply**

$T_A = 0 - 70^{\circ}C$ ; Supply Voltage  $V_{DD} = 3.3 V + -10^{\circ}$

| PARAMETER                      | SYMBOL          | CONDITIONS                     | MIN | TYP | MAX | UNITS |

|--------------------------------|-----------------|--------------------------------|-----|-----|-----|-------|

| Input High Voltage             | V <sub>IH</sub> |                                | 2   |     |     | V     |

| Input Low Voltage              | V <sub>IL</sub> |                                |     |     | 0.8 | V     |

| Input High Current             | I <sub>IH</sub> | $V_{IN} = V_{DD}$              |     | 0.1 | 100 | uA    |

| Input Low Current              | I <sub>IL</sub> | $V_{IN} = 0 V$                 |     | 19  | 50  | uA    |

| Output High Voltage            | Vo <sub>H</sub> | lo <sub>H</sub> = -12 mA       | 2.4 |     |     | V     |

| Output Low Voltage             | VoL             | $Io_L = 12 \text{ mA}$         |     |     | 0.4 | V     |

| Operating Supply<br>Current    | I <sub>DD</sub> | Outputs Unloaded; REF = 66 MHz |     | 30  | 45  | mA    |

|                                |                 |                                |     |     |     |       |

| Powerdown Current              | I <sub>DD</sub> | REF = 0 Mhz                    |     | 0.3 | 12  | uA    |

| Input Frequency                | Fi              |                                | 10  |     | 133 | MHz   |

| Input Capacitance <sup>1</sup> | C <sub>IN</sub> |                                |     |     | 5   | pF    |

NOTES:

1. Guaranteed by design and characterization, not 100% tested in production.

|                                     | , E                   | o pr (unless otherwise specified)             | -    |         |     |       |

|-------------------------------------|-----------------------|-----------------------------------------------|------|---------|-----|-------|

| PARAMETER                           | SYMBOL                | CONDITIONS                                    | MIN  | TYP     | MAX | UNITS |

| Output High Voltage                 | V <sub>OH</sub>       | I <sub>OH</sub> = -12 mA                      | 2.4  |         |     | V     |

| Output Low Voltage                  | V <sub>OL</sub>       | I <sub>OL</sub> = 12 mA                       |      |         | 0.4 | V     |

| Rise Time <sup>1</sup>              | t <sub>r</sub>        | Measure between 0.8 V and 2.0 V               |      | 1.2     | 1.5 | ns    |

| Fall Time <sup>1</sup>              | t <sub>f</sub>        | Measure between 2.0 V and 0.8 V               |      | 1.2     | 1.5 | ns    |

| PLL Lock Time <sup>1</sup>          | TLOCK                 | Stable $V_{DD}$ , valid clock on REF          |      |         | 1   | mS    |

|                                     | f <sub>1</sub>        | C <sub>L</sub> = 30 pF                        | 10   |         | 100 | MHz   |

| Output Frequency                    | f <sub>1</sub>        | C <sub>L</sub> = 10 pF                        | 10   |         | 133 | MHz   |

| Duty Out 1                          | Dt1                   | Measured at 1.4 V, Fout = 66.7 MHz            | 40   | 0 50 60 | %   |       |

| Duty Cycle <sup>1</sup>             | Dt2                   | Measured at $V_{DD}/2$ , Fout < 50.0 MHz      | 45   | 50      | 55  | %     |

| Jitter, Cycle-to-cycle <sup>1</sup> | t <sub>jcyc-cyc</sub> | Measured at 66.7 MHz, loaded outputs          |      |         | 125 | ps    |

| Jitter, Absolute <sup>1</sup>       | Tjabs                 | 10,000 cycles, C <sub>L</sub> = 30 pF         | -100 | 70      | 100 | ps    |

| Jitter, 1-Sigma <sup>1</sup>        | Tj1s                  | 10,000 cycles, C <sub>L</sub> = 30 pF         |      | 14      | 30  | ps    |

| Skew, Group-to-Group <sup>1</sup>   | Tsk                   | Measured at 1.4 V                             |      |         | 215 | ps    |

| Skew, Output-to-Output <sup>1</sup> | Tsk                   | Measured at 1.4 V, within a group             |      |         | 100 | ps    |

| Skew, Device-to-Device <sup>1</sup> | Tdsk-Tdsk             | Measured at V <sub>DD</sub> /2,on CLKOUT pins |      |         | 700 | ps    |

| Delay, Input-to-Output <sup>1</sup> | Dr1                   | Measured at 1.4 V                             |      |         | 700 | ps    |

Electrical Characteristics - Outputs  $T_A = 0 - 70^{\circ}C$ ;  $V_{DD} = 3.3 V +/-10\%$ ;  $C_L = 30 pF$  (unless otherwise specified)

Notes:

1. Guaranteed by design and characterization, not 100% tested in production.

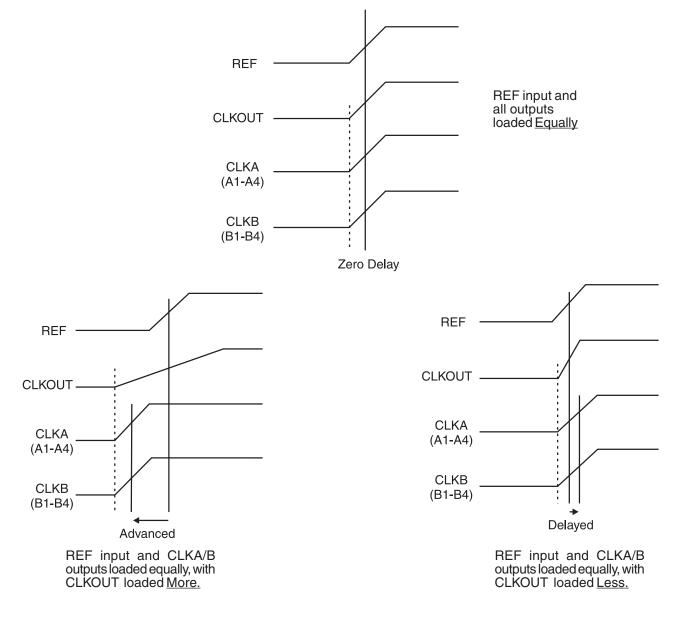

### **Output to Output Skew**

The skew between CLKOUT and the CLKA/B outputs is not dynamically adjusted by the PLL. Since CLKOUT is one of the inputs to the PLL, zero phase difference is maintained from REF to CLKOUT. If all outputs are equally loaded, zero phase difference will maintained from REF to all outputs.

If applications requiring zero output-output skew, all the outputs must equally loaded.

If the CLKA/B outputs are less loaded than CLKOUT, CLKA/B outputs will lead it; and if the CLKA/B is more loaded than CLKOUT, CLKA/B will lag the CLKOUT.

Since the CLKOUT and the CLKA/B outputs are identical, they all start at the same time, but different loads cause them to have different rise times and different times crossing the measurement thresholds.

0093H-12/09/08

#### Timing diagrams with different loading configurations

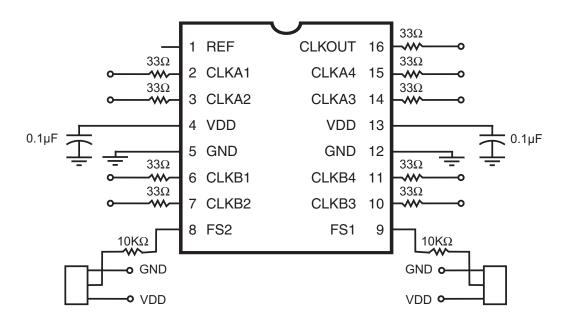

### **Application Suggestion:**

**ICS91309** is a mixed analog/digital product. The analog portion of the PLL is very sensitive to any random noise generated by charging or discharging of internal or external capacitor on the power supply pins. This type of noise will cause excess jitter to the outputs of **ICS91309**. Below is a recommended lay out to alleviate any addition noise. For additional information on FT. layout, please refer to our AN07. The 0.1 uF capacitors should be connected as close as possible to power pins (4 & 13). An Isolated power plane with a 2.2 uF capacitor to ground will enhance the power line stability.

© 2019 Renesas Electronics Corporation

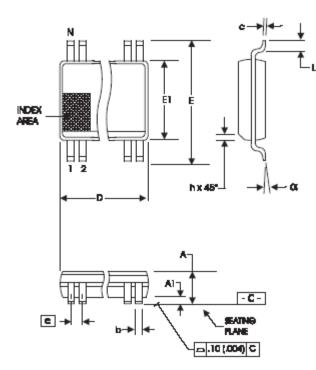

| SYMBOL | In Millimeters In Inches<br>COMMON DIMENSIONS COMMON DIMENSI |        |                |          |

|--------|--------------------------------------------------------------|--------|----------------|----------|

|        | MIN                                                          | MAX    | MIN            | MAX      |

| А      | 1.35                                                         | 1.75   | .053           | .069     |

| A1     | 0.1                                                          | 0.25   | .0040          | .010     |

| A2     | —                                                            | 1.50   | _              | .059     |

| b      | 0.20                                                         | 0.30   | .008           | .012     |

| С      | 0.18                                                         | 0.25   | .007           | .010     |

| D      | SEEVARI                                                      | ATIONS | SEE VARIATIONS |          |

| E      | 5.80                                                         | 6.20   | .228           | .244     |

| E1     | 3.80                                                         | 4.00   | .150           | .157     |

| е      | 0.635                                                        | BASIC  | 0.025          | BASIC    |

| L      | 0.40                                                         | 1.27   | .016           | .050     |

| Ν      | SEEVARI                                                      | ATIONS | SEE VARIATIONS |          |

| α      | 0°                                                           | 8°     | 0°             | 8°       |

| ZD     | SEEVARI                                                      | ATIONS | SEE VAF        | RIATIONS |

VARIATIONS

| Ν                            | D mm. |      | ZD    | D (inch) |                 | ZD    |  |

|------------------------------|-------|------|-------|----------|-----------------|-------|--|

|                              | MIN   | MAX  | (Ref) | MIN      | MAX             | (Ref) |  |

| 16                           | 4.80  | 5.00 | 0.23  | .189     | .197            | .009  |  |

| JEDEC MO-137<br>DOC# 10-0032 |       |      |       |          | 6/1/00<br>REV B |       |  |

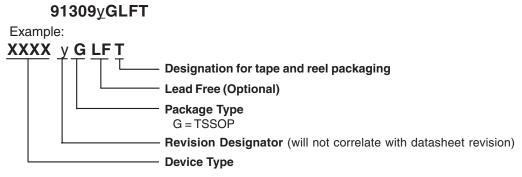

# **Ordering Information**

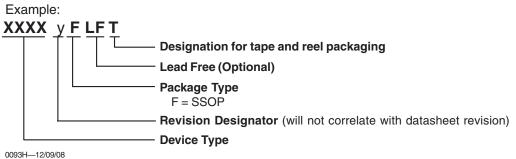

#### 91309¥FLFT

<sup>© 2019</sup> Renesas Electronics Corporation

150 mil (Narrow Body) SOIC

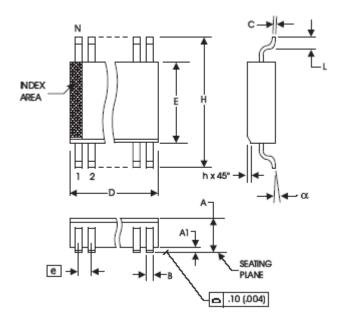

| SYMBOL | In Millimeters<br>COMMON DIMENSIONS |         | In Inches<br>COMMON DIMENSIONS |          |  |

|--------|-------------------------------------|---------|--------------------------------|----------|--|

|        | MIN                                 | MAX     | MIN                            | MAX      |  |

| А      | 1.35                                | 1.75    | .0532                          | .0688    |  |

| A1     | 0.10                                | 0.25    | .0040                          | .0098    |  |

| В      | 0.33                                | 0.51    | .013                           | .020     |  |

| С      | 0.19                                | 0.25    | .0075                          | .0098    |  |

| D      | SEE VARIATIONS                      |         | SEE VARIATIONS                 |          |  |

| E      | 3.80                                | 4.0     | .1497                          | .1574    |  |

| е      | 1.27 E                              | BASIC   | 0.050                          | BASIC    |  |

| Н      | 5.80                                | 6.20    | .2284                          | .2440    |  |

| h      | 0.25                                | 0.50    | .010                           | .020     |  |

| L      | 0.40                                | 1.27    | .016                           | .050     |  |

| Ν      | SEE VAR                             | IATIONS | SEE VAR                        | RIATIONS |  |

| α      | 0°                                  | 8°      | 0°                             | 8°       |  |

VARIATIONS

| Ν  | Dr   | וm.   | D (inch) |       |  |

|----|------|-------|----------|-------|--|

|    | MIN  | MAX   | MIN      | MAX   |  |

| 16 | 9.80 | 10.00 | .3859    | .3937 |  |

### **Ordering Information**

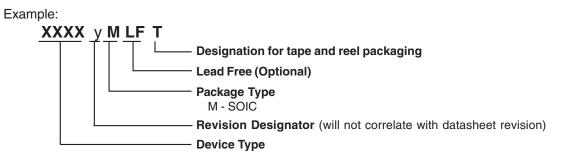

#### 91309yMLFT

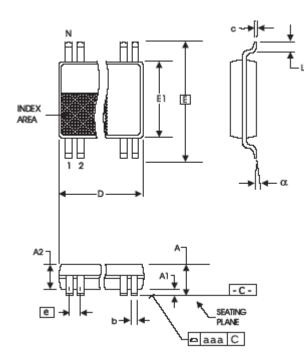

#### 4.40 mm. Body, 0.65 mm. Pitch TSSOP (173 mil) (25.6 mil)

| (173 MI) (25.6 MI) |                |            |              |           |  |  |

|--------------------|----------------|------------|--------------|-----------|--|--|

|                    | In Millimeters |            | In Inches    |           |  |  |

| SYMBOL             | COMMON D       | DIMENSIONS | COMMON D     | IMENSIONS |  |  |

|                    | MIN            | MAX        | MIN          | MAX       |  |  |

| А                  |                | 1.20       |              | .047      |  |  |

| A1                 | 0.05           | 0.15       | .002         | .006      |  |  |

| A2                 | 0.80           | 1.05       | .032         | .041      |  |  |

| b                  | 0.19           | 0.30       | .007         | .012      |  |  |

| С                  | 0.09           | 0.20       | .0035        | .008      |  |  |

| D                  | SEE VAF        | RIATIONS   | SEE VAF      | RIATIONS  |  |  |

| E                  | 6.40           | BASIC      | 0.252 BASIC  |           |  |  |

| E1                 | 4.30           | 4.50       | .169         | .177      |  |  |

| е                  | 0.65           | BASIC      | 0.0256 BASIC |           |  |  |

| L                  | 0.45           | 0.75       | .018         | .030      |  |  |

| N                  | SEE VARIATIONS |            | SEE VAF      | RIATIONS  |  |  |

| α                  | 0°             | 8°         | 0°           | 8°        |  |  |

| aaa                |                | 0.10       |              | .004      |  |  |

VARIATIONS

| Ν  | D mm. |      | D (inch) |      |

|----|-------|------|----------|------|

|    | MIN   | MAX  | MIN      | MAX  |

| 16 | 4.90  | 5.10 | .193     | .201 |

Reference Doc.: JEDEC Publication 95, MO-153 10-0035

### **Ordering Information**

#### **Revision History**

| Rev. | Issue Date | Description                                  | Page # |

|------|------------|----------------------------------------------|--------|

| Н    | 12/9/2008  | Removed ICS prefix from ordering information | 7-9    |

|      |            |                                              |        |

|      |            |                                              |        |

|      |            |                                              |        |

|      |            |                                              |        |

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01 Jan 2024)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <u>www.renesas.com/contact-us/</u>.