#### IDT709149S

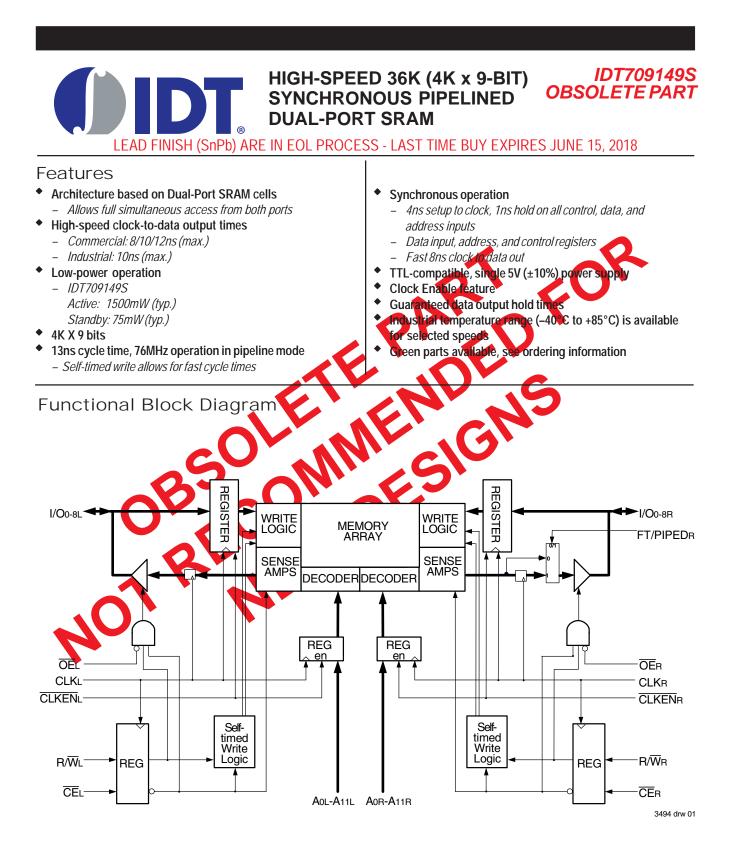

High-Speed 36K (4K x 9-bit) Synchronous Pipelined Dual-Port Static RAM

Industrial and Commercial Temperature Ranges

### Description

The IDT709149 is a high-speed 4K x 9 bit synchronous Dual-Port SRAM. The memory array is based on Dual-Port memory cells to allow simultaneous access from both ports. Registers on control, data, and address inputs provide low set-up and hold times. The timing latitude provided by this approach will allow systems to be designed with very short cycle times. This device has been optimized for applications having unidirectional data flow or bi-directional data flow in bursts, by utilizing input data registers.

A10L

A11L C

N/C C

OEL

Vcc

R/WL C

Vcc 🛛

N/

CEL

GND C

I/O7L □

I/O<sub>6L</sub> ⊏

N/C

10

11

12

13

14

15

16

17

18

19

U U U U U

Pin Configurations<sup>(1,2,3)</sup>

The IDT709149 utilizes a 9-bit wide data path to allow for parity at the user's option. This feature is especially useful in data communication applications where it is necessary to use a parity bit for transmission/ reception error checking.

Fabricated using CMOS high-performance technology, these Dual-Ports typically operate on only 800mW of power at maximum high-speed clock-to-data output times as fast as 8ns. An automatic power down feature, controlled by  $\overline{CE}$ , permits the on-chip circuitry of each port to enter a very low standby power mode.

N/C

A7R

A<sub>8R</sub>

A9R A10R

**A**11R

N/C

**OE**R

GND

J GND

**P**R/WR

N/C פ N/C פ

CER

GND

I/O<sub>8R</sub>

I/O7R

I/O<sub>6R</sub>

N/C

3494 drw 02

FT/PIPEDR

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

The IDT709149 is packaged in an 80-pin TQFP.

#### Reference V/C $A_{6L}$ $A_{8L}$ $A_{9L}$ $A_{9L}$ $A_{9L}$ $A_{6L}$ $A_{6L}$

- 1. All Vcc pins must be connected to power supply.

- 2. All ground pins must be connected to ground supply.

- 3. Package body is approximately 14mm x 14mm x 1.4mm.

- 4, This package code is used to reference the package diagram.

- 5. This text does not indicate the orientaion of the actual part-marking.

IDT709149PF

PN80<sup>(4)</sup>

80-Pin TQFP

Top View<sup>(5)</sup>

21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40

N/C

#### IDT709149S High-Speed 36K (4K x 9-bit) Synchronous Pipelined Dual-Port Static RAM

## Absolute Maximum Ratings<sup>(1)</sup>

| Symbol               | Rating                                     | Commercial<br>& Industrial | Unit        |

|----------------------|--------------------------------------------|----------------------------|-------------|

| Vterm <sup>(2)</sup> | Terminal Voltage<br>with Respect<br>to GND | -0.5 to +7.0               | V           |

| Vterm <sup>(2)</sup> | Terminal Voltage                           | -0.5 to Vcc                | V           |

| Tbias                | Temperature<br>Under Bias                  | -55 to +125                | ٥C          |

| Tstg                 | Storage<br>Temperature                     | -65 to +150                | ٥C          |

| Ιουτ                 | DC Output Current                          | 50                         | mA          |

|                      | -                                          |                            | 3494 tbl 01 |

#### NOTES:

Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

VTERM must not exceed Vcc + 10% for more than 25% of the cycle time or 10ns maximum, and is limited to ≤ 20mA for the period of VTERM ≥ Vcc + 10%.

## Capacitance ( $TA = +25^{\circ}C$ , f = 1.0MHz)

| Symbol | Parameter          | Conditions | Max. | Unit        |

|--------|--------------------|------------|------|-------------|

| Cin    | Input Capacitance  | VIN = 3dV  | 8    | pF          |

| Соит   | Output Capacitance | Vout = 3dV | 9    | pF          |

|        |                    |            |      | 3494 tbl 04 |

#### NOTES:

These parameters are determined by device characterization, but are not production tested.

3dV references the interpolated capacitance when the input and output switch from 0V to 3V or from 3V to 0V.

## Maximum Operating Temperature and Supply Voltage<sup>(1)</sup>

| Grade      | Ambient Temperature | GND | Vcc               |

|------------|---------------------|-----|-------------------|

| Commercial | 0°C to +70°C        | 0V  | 5.0V <u>+</u> 10% |

| Industrial | -40°C to +85°C      | 0V  | 5.0V <u>+</u> 10% |

|            |                     |     | 3494 tbl 02       |

NOTES:

1. This is the parameter TA. This is the "instant on" case temperature.

## Recommended DC Operating Conditions

| Symbol | Parameter          | Min.                | Тур. | Max.               | Unit |

|--------|--------------------|---------------------|------|--------------------|------|

| Vcc    | Supply Voltage     | 4.5                 | 5.0  | 5.5                | V    |

| GND    | Ground             | 0                   | 0    | 0                  | V    |

| V⊮     | Input High Voltage | 2.2                 |      | 6.0 <sup>(2)</sup> | V    |

| VIL    | Input Low Voltage  | -0.5 <sup>(1)</sup> |      | 0.8                | V    |

#### NOTES:

1. VIL  $\geq$  -1.5V for pulse width less than 10ns.

2. VTERM must not exceed Vcc + 10%.

## DC Electrical Characteristics Over the Operating Temperature and Supply Voltage Range (Vcc = 5.0V ± 10%)

|        |                                      |                                 | 709149S |      |             |

|--------|--------------------------------------|---------------------------------|---------|------|-------------|

| Symbol | Parameter                            | Test Conditions                 | Min.    | Max. | Unit        |

| LI     | Input Leakage Current <sup>(1)</sup> | Vcc = 5.5V, $VIN$ = 0V to $Vcc$ | —       | 10   | μA          |

| LO     | Output Leakage Current               | Vout = 0V to Vcc                |         | 10   | μA          |

| Vol    | Output Low Voltage                   | IOL = +4mA                      |         | 0.4  | V           |

| Vон    | Output High Voltage                  | Юн = -4mA                       | 2.4     | _    | V           |

| OTE    |                                      |                                 |         |      | 3494 tbl 05 |

#### NOTE:

1. At Vcc  $\leq$  2.0V, input leakages are undefined

3494 tbl 03

High-Speed 36K (4K x 9-bit) Synchronous Pipelined Dual-Port Static RAM

Industrial and Commercial Temperature Ranges

## DC Electrical Characteristics Over the Operating Temperature and Supply Voltage Range<sup>(4)</sup> ( $Vcc = 5V \pm 10\%$ )

|              |                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                           |         | 709149S8<br>Com'l Only |      | Co   | 49S10<br>m'l<br>Ind | 709149S12<br>Com'l Only |      |      |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------------------|------|------|---------------------|-------------------------|------|------|

| Symbol       | Parameter                                                                                                                                                                                       | Test Condition                                                                                                                                                                                                                                                            | Version | Тур.                   | Мах. | Тур. | Max.                | Тур.                    | Max. | Unit |

| lcc          | Dynamic Operating<br>Current                                                                                                                                                                    | $\overline{CE}$ L and $\overline{CE}R = VIL$ ,                                                                                                                                                                                                                            |         | 200                    | 320  | 190  | 310                 | 180                     | 300  | mA   |

|              | (Both Ports Active)                                                                                                                                                                             | Outputs Disabled<br>$f = f_{MAX}^{(1)}$                                                                                                                                                                                                                                   | IND     |                        |      | 190  | 340                 |                         |      |      |

| <b>I</b> SB1 | Standby Current                                                                                                                                                                                 | $\overline{CE}_{L}$ and $\overline{CE}_{R} = V_{H}$                                                                                                                                                                                                                       | COM'L   | 100                    | 150  | 90   | 150                 | 85                      | 140  | mA   |

|              | (Both Ports - TTL<br>Level Inputs)                                                                                                                                                              | $f = f MAX^{(1)}$                                                                                                                                                                                                                                                         | IND     |                        |      | 90   | 175                 |                         |      |      |

| ISB2         | Standby Current<br>(One Port - TTL                                                                                                                                                              | $\label{eq:cellson} \overline{CE}^* \mathbb{A}^* = V_{IL} \mbox{ and } \overline{CE}^* \mathbb{B}^* = V_{IH}^{(3)} \\ \mbox{ Active Port Outputs Disabled,} \\ f = f_{MAX}^{(1)}$                                                                                         | COM'L   | 180                    | 230  | 170  | 220                 | 160                     | 210  | mA   |

|              | Level Inputs)                                                                                                                                                                                   |                                                                                                                                                                                                                                                                           | IND     |                        |      | 170  | 250                 |                         |      |      |

| ISB3         | Full Standby Current<br>(Both Ports - All                                                                                                                                                       | CEL and<br>CER ≥ Vcc - 0.2V,                                                                                                                                                                                                                                              | COM'L   | 5                      | 15   | 5    | 15                  | 5                       | 15   | mA   |

|              | $\begin{array}{l} \mbox{CMOS Level Inputs)} \\ \mbox{V}_{\mathbb{N}} \geq \mbox{V}_{CC} - 0.2 \mbox{V} \mbox{ or } \\ \mbox{V}_{\mathbb{N}} \leq 0.2 \mbox{V}, \mbox{ f} = 0^{(2)} \end{array}$ |                                                                                                                                                                                                                                                                           | IND     | _                      | _    | 5    | 20                  |                         |      |      |

| ISB4         | Full Standby Current $\overline{CE}^*A^* \leq 0.2V$ and                                                                                                                                         |                                                                                                                                                                                                                                                                           | COM'L   | 170                    | 220  | 160  | 210                 | 150                     | 200  | mA   |

|              | (One Port - All<br>CMOS Level Inputs)                                                                                                                                                           | $\label{eq:central_constraint} \begin{array}{ c c c c c } \hline \overline{C} E_{B^*} & \overline{\geq} & Vcc & - 0.2 V^{(3)} \\ \hline V & \geq & Vcc & - 0.2 V \text{ or } V & N & \leq 0.2 V \\ \hline Active Port Outputs Disabled, \\ f &= & fmax^{(1)} \end{array}$ | IND     |                        |      | 160  | 240                 |                         |      |      |

NOTES:

3494 tbl 06

1. At f = fMax, address and control lines (except Output Enable) are cycling at the maximum frequency clock cycle of 1/tcLK, using "AC TEST CONDITIONS" at input levels of GND to 3V.

2. f = 0 means no address, clock, or control lines change. Applies only to input at CMOS level standby.

3. Port "A" may be either left or right port. Port "B" is the opposite from port "A".

4. Vcc = 5V, TA = 25°C for Typ, and are not production tested. Icc pc = 150mA (Typ).

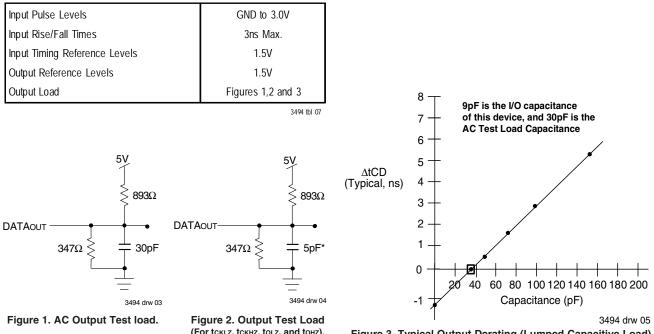

## AC Test Conditions

(For tcklz, tckHz, tolz, and toHz). \*Including scope and jig.

Figure 3. Typical Output Derating (Lumped Capacitive Load).

## AC Electrical Characteristics Over the Operating Temperature Range-(Read and Write Cycle Timing)

|        |                                                   |    | 709149S8 709149S10<br>Com'l Only Com'l<br>& Ind |      |      |      | 709149S12<br>Com'l Only |      |

|--------|---------------------------------------------------|----|-------------------------------------------------|------|------|------|-------------------------|------|

| Symbol | Parameter Min.                                    |    | Max.                                            | Min. | Max. | Min. | Max.                    | Unit |

| tcyc1  | Clock Cycle Time (Flow-Through) <sup>(3)</sup>    | 16 |                                                 | 20   |      | 20   | —                       | ns   |

| tcyc2  | Clock Cycle Time (Pipelined) <sup>(3)</sup>       | 13 |                                                 | 15   |      | 16   | —                       | ns   |

| tCH1   | Clock High Time (Flow-Through) <sup>(3)</sup>     | 6  |                                                 | 7    |      | 8    | —                       | ns   |

| tal1   | Clock Low Time (Flow-Through) <sup>(3)</sup>      | 6  |                                                 | 7    |      | 8    | _                       | ns   |

| tCH2   | Clock High Time (Pipelined) <sup>(3)</sup>        | 6  |                                                 | 6    |      | 6    | _                       | ns   |

| tCL2   | Clock Low Time (Pipelined) <sup>(3)</sup>         | 6  |                                                 | 6    |      | 6    | _                       | ns   |

| tCD1   | Clock to Data Valid (Flow-Through) <sup>(3)</sup> |    | 12                                              |      | 15   |      | 20                      | ns   |

| tCD2   | Clock to Data Valid (Pipelined)(3)                | _  | 8                                               | —    | 10   |      | 12                      | ns   |

| ts     | Registered Signal Set-up Time                     | 4  |                                                 | 4    |      | 5    | —                       | ns   |

| tн     | Registered Signal Hold Time                       | 1  |                                                 | 1    |      | 1    | _                       | ns   |

| tDC    | Data Output Hold After Clock High                 | 1  |                                                 | 1    |      | 1    |                         | ns   |

| tcklz  | Clock High to Output Low-Z <sup>(1,2)</sup>       | 2  |                                                 | 2    |      | 2    |                         | ns   |

| tскнz  | Clock High to Output High-Z <sup>(1,2)</sup>      |    | 7                                               |      | 7    |      | 9                       | ns   |

| toe    | Output Enable to Output Valid                     | _  | 8                                               |      | 8    |      | 10                      | ns   |

| tolz   | Output Enable to Output Low-Z <sup>(1,2)</sup>    | 0  |                                                 | 0    |      | 0    | —                       | ns   |

| tонz   | Output Disable to Output High-Z <sup>(1,2)</sup>  | _  | 7                                               |      | 7    |      | 9                       | ns   |

| tscк   | Clock Enable, Disable Set-Up Time                 | 4  |                                                 | 4    |      | 5    | —                       | ns   |

| tнск   | Clock Enable, Disable Hold Time                   | 1  |                                                 | 1    |      | 1    | —                       | ns   |

| tcwdd  | Write Port Clock High to Read Data Delay          |    | 25                                              |      | 30   |      | 35                      | ns   |

3494 tbl 08

#### NOTES:

1. Transition is measured 0mV from Low or High-impedance voltage with the Output Test Load (Figure 2).

2. This parameter is guaranteed by device characterization, but is not production tested.

3. The Pipelined output parameters (tcvc2, tcp2) always apply to the Left Port. The Right Port uses the Pipelined tcvc2 and tcp2 when FT/PIPEDR = VIH and the Flow-Through parameters (tcyc1, tcp1) when FT/PIPEDR = VIL.

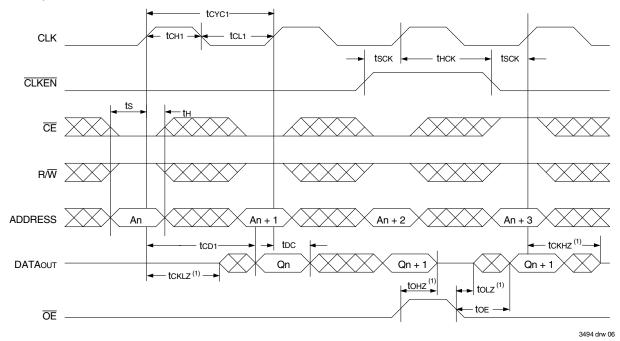

Timing Waveform of Read Cycle for Flow-Through Output on Right Port (FT/Piped<sub>R</sub> = VIL)

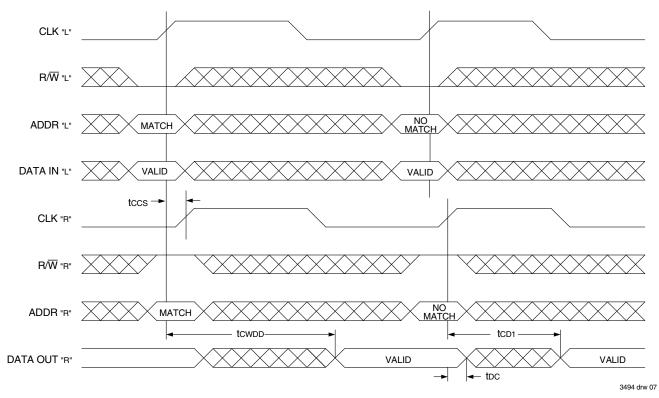

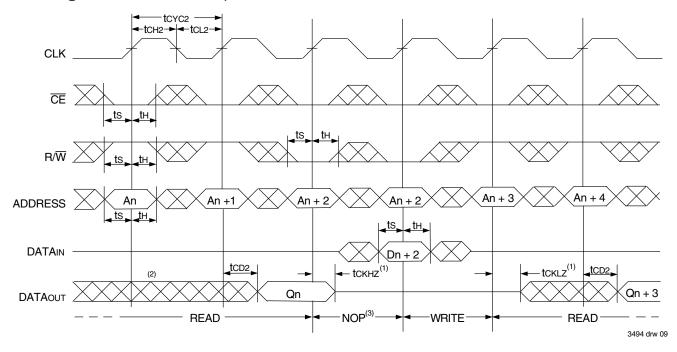

Timing Waveform of Left Port Write to Flow-Through Right Port Read  $(FT/Piped_R = VIL)^{(2,3)}$

NOTES:

- 2.  $\overline{CE}_{L} = \overline{CE}_{R} = V_{IL}, \overline{CLKEN}_{L} = \overline{CLKEN}_{R} = V_{IL}$

- 3.  $\overline{OE} = VIL$  for the reading port, port 'R'.

<sup>1.</sup> Transition is measured 0mV from Low or High-impedance voltage with the Output Test Load (Figure 2).

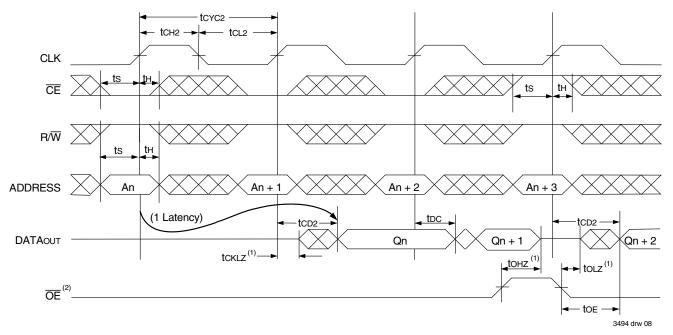

# Timing Waveform of Read Cycle for Pipelined Operation (Left Port; Right Port when FT/Piped<sub>R</sub> = VIH)<sup>(3)</sup>

NOTES:

- 1. Transition is measured 0mV from Low or High-impedance voltage with the Output Test Load (Figure 2).

- 2. OE is asynchronously controlled; all other inputs are synchronous to the rising clock edge.

- 3.  $\overline{\text{CLKENL}}$  and  $\overline{\text{CLKENR}} = \text{VIL}$ .

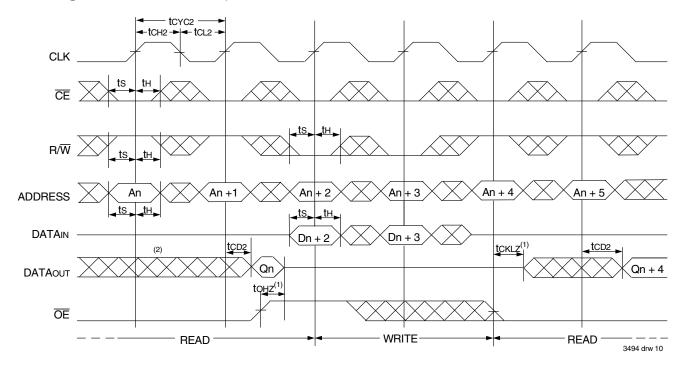

Timing Waveform of Pipelined Read-to-Write-to-Read ( $\overline{OE} = VIL$ )

Timing Waveform of Pipelined Read-to-Write-to-Read (**OE** Controlled)

#### NOTES:

- 1. Transition is measured 0mV from Low or High-impedance voltage with the Output Test Load (Figure 2).

- 2. Output state (High, Low, or High-impedance) is determined by the previous cycle control signals.

- 3. "NOP" is "No Operation." Data in memory at the selected address may be corrupted and should be re-written to guarantee data integrity.

#### IDT709149S

High-Speed 36K (4K x 9-bit) Synchronous Pipelined Dual-Port Static RAM

Industrial and Commercial Temperature Ranges

## **Functional Description**

The IDT709149 provides a true synchronous Dual-Port Static RAM interface. Registered inputs provide very short set-up and hold times on address, data, and all critical control inputs. All internal registers are clocked on the rising edge of the clock signal. An asynchronous output enable is provided to ease asynchronous bus interfacing.

The internal write pulse width is dependent only on the low to high transitions of the clock signal to initiate a write allowing the shortest

possible realized cycle times. Clock enable inputs are provided to stall the operation of the address and data input registers without introducing clock skew for very fast interleaved memory applications.

A HIGH on the  $\overline{CE}$  input for one clock cycle will power down the internal circuitry to reduce static power consumption.

When piplelined mode is enabled, two cycles are required with  $\overline{\text{CE}}$  LOW to reactivate the outputs.

## Truth Table I: Read/Write Control<sup>(1)</sup>

| Inputs     |         | Outputs          |              |         |                                                        |

|------------|---------|------------------|--------------|---------|--------------------------------------------------------|

| Syn        | chronou | s <sup>(3)</sup> | Asynchronous |         |                                                        |

| CLK        | ĒĒ      | R/W              | ŌĒ           | I/O0-8  | Mode                                                   |

| $\uparrow$ | Н       | Х                | Х            | High-Z  | Deselected—Power Down                                  |

| $\uparrow$ | L       | L                | Х            | DATAIN  | Selected and Write Enable                              |

| $\uparrow$ | L       | Н                | L            | DATAOUT | Read Selected and Data Output Enabled Read (1 Latency) |

| $\uparrow$ | Х       | Х                | Н            | High-Z  | Data I/O Disabled                                      |

3494 tbl 09

3494 tbl 10

## Truth Table II: Clock Enable Function Table<sup>(1)</sup>

|                   | Inputs             |                      | Registe | r Inputs | Register Outputs <sup>(4)</sup> |         |  |

|-------------------|--------------------|----------------------|---------|----------|---------------------------------|---------|--|

| Operating Mode    | CLK <sup>(3)</sup> | CLKEN <sup>(2)</sup> | ADDR    | DATAIN   | ADDR                            | DATAOUT |  |

| Load "1"          | $\uparrow$         | L                    | Н       | Н        | Н                               | Н       |  |

| Load "0"          | $\uparrow$         | L                    | L       | L        | L                               | L       |  |

| Hold (do nothing) | $\uparrow$         | Н                    | Х       | Х        | NC                              | NC      |  |

|                   | Х                  | Н                    | Х       | Х        | NC                              | NC      |  |

#### NOTES:

'H' = HIGH voltage level steady state, 'h' = HIGH voltage level one set-up time prior to the LOW-to-HIGH clock transition, 'L' = LOW voltage level steady state 'l' = LOW voltage level one set-up time prior to the LOW-to-HIGH clock transition, 'X' = Don't care, 'NC' = No change

2. CLKEN = VIL must be clocked in during Power-Up.

3. Control signals are initialted and terminated on the rising edge of the CLK, depending on their input level. When R/W and  $\overline{CE}$  are LOW, a write cycle is initiated on the LOW-to-HIGH transition of the CLK. Termination of a write cycle is done on the next LOW-to-HIGH transistion of the CLK.

4. The register outputs are internal signals from the register inputs being clocked in or disabled by CLKEN.

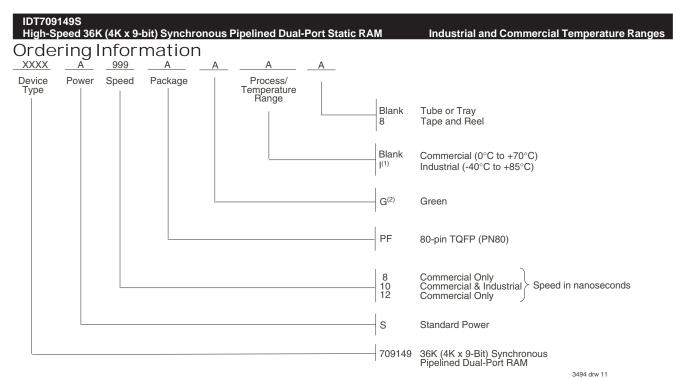

#### NOTES:

- 1. Contact your local sales office for industrial temp range for other speeds, packages and powers.

- 2. Green parts available. For specific speeds, packages and powers contact your local sales office.

- LEAD FINISH (SnPb) parts are in EOL process. Product Discontinuation Notice PDN# SP-17-02

## Datasheet Document History

| 3/8/99:   | Initiated datasheet document history                                                                         |  |  |  |  |  |  |

|-----------|--------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|           | Converted to new format                                                                                      |  |  |  |  |  |  |

|           | Cosmetic and typographical corrections                                                                       |  |  |  |  |  |  |

|           | Added additional notes to pin configurations                                                                 |  |  |  |  |  |  |

| 6/3/99:   | Changed drawing format                                                                                       |  |  |  |  |  |  |

| 9/1/99:   | Removed Preliminary                                                                                          |  |  |  |  |  |  |

| 11/10/99: | Replaced IDT logo                                                                                            |  |  |  |  |  |  |

| 5/24/00:  | Page 3 Increased storage temperature parameter                                                               |  |  |  |  |  |  |

|           | Clarified TA parameter                                                                                       |  |  |  |  |  |  |

|           | Page 5 DC Electrical parameters-changed wording from "open" to "disabled"                                    |  |  |  |  |  |  |

|           | Changed ±200mV to 0mV in notes                                                                               |  |  |  |  |  |  |

| 01/24/02: | Page 2 Added date revision for pin configuration                                                             |  |  |  |  |  |  |

|           | Page 3, 4 & 5 Removed Industrial temp footnote from all tables                                               |  |  |  |  |  |  |

|           | Page 4 Added Industrial temp to 10ns speed in the column heading and values of DC Electrical Characteristics |  |  |  |  |  |  |

|           | Page 5 Corrected a typo in the column heading of AC Electrical Characteristics                               |  |  |  |  |  |  |

|           | Page 5 Added Industrial temp to 10ns speed in the column heading of AC Electrical Characteristics            |  |  |  |  |  |  |

|           | Page 10 Added Industrial temp to 10ns offering in ordering information                                       |  |  |  |  |  |  |

|           | Pages 1& 10 Replaced TM logo with ® logo                                                                     |  |  |  |  |  |  |

| 01/29/09: | Page 10 Removed "IDT" from orderable part number                                                             |  |  |  |  |  |  |

| 04/08/15: | Page 2 Removed IDT in reference to fabrication                                                               |  |  |  |  |  |  |

|           | Page 2 &10 The package code PN80-1 changed to PN80 to match standard package codes                           |  |  |  |  |  |  |

|           | Page 4 Corrected typo in the Typical Output Derating(Lumped Capitive Load) diagram                           |  |  |  |  |  |  |

| 02/02/18: | Page 10 Added Tape and Reel and Green indicators with their footnote annotations to the Ordering Information |  |  |  |  |  |  |

| 02/02/10. | Product Discontinuation Notice - PDN# SP-17-02                                                               |  |  |  |  |  |  |

|           | Last time buy expires June 15, 2018                                                                          |  |  |  |  |  |  |

| 03/05/20: | 709149 Datasheet changed to Obsolete Status                                                                  |  |  |  |  |  |  |

|           | CORPORATE HEADOUARTERS   for SALES   for Tech Support                                                        |  |  |  |  |  |  |

for SALES: 800-345-7015 or 408-284-8200 fax: 408-284-2775 www.idt.com *for Tech Support:* 408-284-2794 DualPortHelp@idt.com

The IDT logo is a registered trademark of Integrated Device Technology, Inc.

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01 Jan 2024)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <u>www.renesas.com/contact-us/</u>.