### カタログ等資料中の旧社名の扱いについて

2010年4月1日を以ってNECエレクトロニクス株式会社及び株式会社ルネサステクノロジが合併し、両社の全ての事業が当社に承継されております。従いまして、本資料中には旧社名での表記が残っておりますが、当社の資料として有効ですので、ご理解の程宜しくお願い申し上げます。

ルネサスエレクトロニクス ホームページ (http://www.renesas.com)

2010年4月1日 ルネサスエレクトロニクス株式会社

【発行】ルネサスエレクトロニクス株式会社(http://www.renesas.com)

【問い合わせ先】http://japan.renesas.com/inquiry

#### ご注意書き

- 1. 本資料に記載されている内容は本資料発行時点のものであり、予告なく変更することがあります。当社製品のご購入およびご使用にあたりましては、事前に当社営業窓口で最新の情報をご確認いただきますとともに、当社ホームページなどを通じて公開される情報に常にご注意ください。

- 2. 本資料に記載された当社製品および技術情報の使用に関連し発生した第三者の特許権、著作権その他の知的 財産権の侵害等に関し、当社は、一切その責任を負いません。当社は、本資料に基づき当社または第三者の 特許権、著作権その他の知的財産権を何ら許諾するものではありません。

- 3. 当社製品を改造、改変、複製等しないでください。

- 4. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。お客様の機器の設計において、回路、ソフトウェアおよびこれらに関連する情報を使用する場合には、お客様の責任において行ってください。これらの使用に起因しお客様または第三者に生じた損害に関し、当社は、一切その責任を負いません。

- 5. 輸出に際しては、「外国為替及び外国貿易法」その他輸出関連法令を遵守し、かかる法令の定めるところにより必要な手続を行ってください。本資料に記載されている当社製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的その他軍事用途の目的で使用しないでください。また、当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器に使用することができません。

- 6. 本資料に記載されている情報は、正確を期すため慎重に作成したものですが、誤りがないことを保証するものではありません。万一、本資料に記載されている情報の誤りに起因する損害がお客様に生じた場合においても、当社は、一切その責任を負いません。

- 7. 当社は、当社製品の品質水準を「標準水準」、「高品質水準」および「特定水準」に分類しております。また、各品質水準は、以下に示す用途に製品が使われることを意図しておりますので、当社製品の品質水準をご確認ください。お客様は、当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途に当社製品を使用することができません。また、お客様は、当社の文書による事前の承諾を得ることなく、意図されていない用途に当社製品を使用することができません。当社の文書による事前の承諾を得ることなく、「特定水準」に分類された用途または意図されていない用途に当社製品を使用したことによりお客様または第三者に生じた損害等に関し、当社は、一切その責任を負いません。なお、当社製品のデータ・シート、データ・ブック等の資料で特に品質水準の表示がない場合は、標準水準製品であることを表します。

標準水準: コンピュータ、OA 機器、通信機器、計測機器、AV 機器、家電、工作機械、パーソナル機器、 産業用ロボット

高品質水準:輸送機器(自動車、電車、船舶等)、交通用信号機器、防災・防犯装置、各種安全装置、生命 維持を目的として設計されていない医療機器(厚生労働省定義の管理医療機器に相当)

特定水準: 航空機器、航空宇宙機器、海底中継機器、原子力制御システム、生命維持のための医療機器(生命維持装置、人体に埋め込み使用するもの、治療行為(患部切り出し等)を行うもの、その他直接人命に影響を与えるもの)(厚生労働省定義の高度管理医療機器に相当)またはシステム

- 8. 本資料に記載された当社製品のご使用につき、特に、最大定格、動作電源電圧範囲、放熱特性、実装条件その他諸条件につきましては、当社保証範囲内でご使用ください。当社保証範囲を超えて当社製品をご使用された場合の故障および事故につきましては、当社は、一切その責任を負いません。

- 9. 当社は、当社製品の品質および信頼性の向上に努めておりますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は耐放射線設計については行っておりません。当社製品の故障または誤動作が生じた場合も、人身事故、火災事故、社会的損害などを生じさせないようお客様の責任において冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、機器またはシステムとしての出荷保証をお願いいたします。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様が製造された最終の機器・システムとしての安全検証をお願いいたします。

- 10. 当社製品の環境適合性等、詳細につきましては製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、当社は、一切その責任を負いません。

- 11. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを固くお断りいたします。

- 12. 本資料に関する詳細についてのお問い合わせその他お気付きの点等がございましたら当社営業窓口までご 照会ください。

- 注1. 本資料において使用されている「当社」とは、ルネサスエレクトロニクス株式会社およびルネサスエレクトロニクス株式会社がその総株主の議決権の過半数を直接または間接に保有する会社をいいます。

- 注 2. 本資料において使用されている「当社製品」とは、注 1 において定義された当社の開発、製造製品をいいます。

改訂一覧は表紙をクリックして直接ご覧になれます。 改訂一覧は改訂箇所をまとめたものであり、詳細については、 必ず本文の内容をご確認ください。

# H8/38076Rグループ

ハードウェアマニュアル ルネサス16ビットシングルチップマイクロコンピュータ H8ファミリ/ H8/300H Super Low Powerシリーズ

> H8/38076RF H8/38076R H8/38075R H8/38074R H8/38073R

#### 安全設計に関するお願い -

1. 弊社は品質、信頼性の向上に努めておりますが、半導体製品は故障が発生したり、 誤動作する場合があります。弊社の半導体製品の故障又は誤動作によって結果として、人身事故、火災事故、社会的損害などを生じさせないような安全性を考慮した 冗長設計、延焼対策設計、誤動作防止設計などの安全設計に十分ご留意ください。

#### ■ 本資料ご利用に際しての留意事項 -

- 1. 本資料は、お客様が用途に応じた適切なルネサステクノロジ製品をご購入いただくための参考資料であり、本資料中に記載の技術情報についてルネサステクノロジが所有する知的財産権その他の権利の実施、使用を許諾するものではありません。

- 2. 本資料に記載の製品データ、図、表、プログラム、アルゴリズムその他応用回路例の使用に起因する損害、第三者所有の権利に対する侵害に関し、ルネサステクノロジは責任を負いません。

- 3. 本資料に記載の製品データ、図、表、プログラム、アルゴリズムその他全ての情報 は本資料発行時点のものであり、ルネサステクノロジは、予告なしに、本資料に記載した製品または仕様を変更することがあります。ルネサステクノロジ半導体製品のご購入に当たりましては、事前にルネサステクノロジ、ルネサス販売または特約店へ最新の情報をご確認頂きますとともに、ルネサステクノロジホームページ (http://www.renesas.com) などを通じて公開される情報に常にご注意ください。

- 4. 本資料に記載した情報は、正確を期すため、慎重に制作したものですが万一本資料の記述誤りに起因する損害がお客様に生じた場合には、ルネサステクノロジはその責任を負いません。

- 5. 本資料に記載の製品データ、図、表に示す技術的な内容、プログラム及びアルゴリズムを流用する場合は、技術内容、プログラム、アルゴリズム単位で評価するだけでなく、システム全体で十分に評価し、お客様の責任において適用可否を判断してください。ルネサステクノロジは、適用可否に対する責任は負いません。

- 6. 本資料に記載された製品は、人命にかかわるような状況の下で使用される機器あるいはシステムに用いられることを目的として設計、製造されたものではありません。本資料に記載の製品を運輸、移動体用、医療用、航空宇宙用、原子力制御用、海底中継用機器あるいはシステムなど、特殊用途へのご利用をご検討の際には、ルネサステクノロジ、ルネサス販売または特約店へご照会ください。

- 7. 本資料の転載、複製については、文書によるルネサステクノロジの事前の承諾が必要です。

- 8. 本資料に関し詳細についてのお問い合わせ、その他お気付きの点がございましたらルネサステクノロジ、ルネサス販売または特約店までご照会ください。

### 製品に関する一般的注意事項

#### 1. NC 端子の処理

【注意】NC 端子には、何も接続しないようにしてください。

NC(Non-Connection)端子は、内部回路に接続しない場合の他、テスト用端子やノイズ軽減などの目的で使用します。このため、NC 端子には、何も接続しないようにしてください。 接続された場合については保証できません。

2. 未使用入力端子の処理

【注意】未使用の入力端子はハイまたはローレベルに固定してください。

CMOS 製品の入力端子は、一般にハイインピーダンス入力となっています。未使用端子を開放状態で動作させると、周辺ノイズの誘導により中間レベルが発生し、内部で貫通電流が流れて誤動作を起こす恐れがあります。未使用の入力端子は、ハイまたはローレベルに固定してください。

3. 初期化前の処置

【注意】電源投入時は、製品の状態は不定です。

すべての電源に電圧が印加され、リセット端子にローレベルが入力されるまでの間、内部回路は不確定であり、レジスタの設定や各端子の出力状態は不定となります。この不定状態によってシステムが誤動作を起こさないようにシステム設計を行ってください。リセット機能を持つ製品は、電源投入後は、まずリセット動作を実行してください。

4. 未定義・リザーブアドレスのアクセス禁止

【注意】未定義・リザーブアドレスのアクセスを禁止します。

未定義・リザーブアドレスは、将来の機能拡張用の他、テスト用レジスタなどが割り付けられている場合があります。これらのレジスタをアクセスしたときの動作および継続する動作については、 保証できませんので、アクセスしないようにしてください。

## 本書の構成

本書は、以下の構成で制作しています。

- 1. 製品に関する一般的注意事項

- 2. 本書の構成

- 3. はじめに

- 4. 目次

- 5. 概要

- 6. 各機能モジュールの説明

- ・CPU およびシステム制御系

- ・内蔵周辺モジュール

各モジュールの機能説明の構成は、モジュール毎に異なりますが、一般的には、 特長、 入出力端子、 レジスタの説明、 動作説明、 使用上の注意事項、 等の節で構成されています。

本 LSI を用いた応用システムを設計する際、注意事項を十分確認の上設計してください。 各章の本文中には説明に対する注意事項と、各章の最後には使用上の注意事項があります。 必ずお読みください。(使用上の注意事項は必要により記載されます。)

- 7. レジスター覧

- 8. 電気的特性

- 9. 付録

- 10. 本版で改訂された箇所(改訂版のみ適用)

改訂来歴は、前版の記載内容について訂正・追加された主な箇所についてまとめたものです。 改訂内容の全てについて記載したものではありませんので、詳細については、本書の本文上で ご確認ください。

11. 索引

## はじめに

H8/38076R グループは、ルネサスオリジナルの高速 H8/300H CPU をコアにして、システム構成に必要な周辺機能を集積したシングルチップマイクロコンピュータです。H8/300H CPU は、H8/300 CPU と互換性のある命令体系を備えています。

- 対象者 このマニュアルは、H8/38076R グループを用いた応用システムを設計するユーザを対象としています。 このマニュアルを使用される読者には、電気回路、論理回路、およびマイクロコンピュータに関する 基本的な知識を必要とします。

- 目的 このマニュアルは、H8/38076R グループのハードウェア機能と電気的特性をユーザに理解していただくことを目的にしています。なお、実行命令の詳細については、「H8/300H シリーズ プログラミングマニュアル」に記載しておりますので、あわせてご覧ください。

#### 読み方

• 機能全体を理解しようとするとき。

目次にしたがって読んでください。

本書は、大きく分類すると、CPU、システム制御機能、周辺機能、電気的特性の順に構成されています。

• CPU機能の詳細を理解したいとき。

別冊の「H8/300Hシリーズ プログラミングマニュアル」を参照してください。

レジスタ名がわかっていて、詳細機能を知りたいとき。

本書の後ろに、「索引」があります。索引からページ番号を検索してください。

「第23章 レジスタ一覧」にアドレス、ビット内容、初期化についてまとめています。

#### レジスタ表記

シリアルコミュニケーションインタフェースなど、同一または類似した機能が複数チャネルに存在する場合 に次の表記を使用します。

XXX\_N (XXXは基本レジスタ名称、Nはチャネル番号)

凡例 ビット表記順 :左側が上位ビット、右側が下位ビットの順に表記しています。

#### ご注意

オンチップデバッギングエミュレータ (E7) を使用して H8/38076R のプログラム開発、デバッグを行う場合、以下の制限事項がありますのでご注意ください。

- 1. NMI端子はオンチップデバッギングエミュレータで占有するため使用できません。

- 2. P16、P36、P37端子も使用できません。使用する場合はユーザ基板上に追加ハードウェアが必要となります。

- 3. アドレスH'D000~H'DFFF領域はオンチップデバッギングエミュレータで使用するためユーザはこの領域は使用できません。

- 4. アドレスH'F380~H'F77F領域は絶対にアクセスしないでください。

- 5. オンチップデバッギングエミュレータを使用する場合、アドレスブレークをオンチップデバッギングエミュレータが使用するか、ユーザに開放するか設定可能になっています。オンチップデバッギングエミュレータがアドレスブレークを使用する場合、ユーザはアドレスブレークの制御レジスタをアクセスしないでください。

- 6. オンチップデバッギングエミュレータ使用時、NMI端子は入力、P16端子およびP36端子は入力、P37端子は出力になります。

- 7. ブートモードによるオンボードプログラミングモードでは、SCI3のチャネル1 ( P41/RXD、P42/TXD ) を使用します。

- 8. オンチップデバッギングエミュレータ使用時、クロック停止レジスタ1のビット1 (FROMCKSTP) は必ず1 にセットしてください。

関連資料一覧 ウェブ・サイトに最新資料を掲載しています。ご入手の資料が最新版であるかを確認してください。 (http://japan.renesas.com/)

• H8/38076Rグループに関するユーザーズマニュアル

| 資料名                        | 資料番号       |

|----------------------------|------------|

| H8/38076R グループ ハードウェアマニュアル | 本マニュアル     |

| H8/300H シリーズ プログラミングマニュアル  | RJJ09B0141 |

#### • 開発ツール関連ユーザーズマニュアル

| 資料名                                                             | 資料番号            |

|-----------------------------------------------------------------|-----------------|

| H8S、H8/300 シリーズ C/C++コンパイラ、アセンブラ、最適化リンケージエディタ                   | RJJ10B0049      |

| ユーザーズマニュアル                                                      |                 |

| H8S、H8/300 シリーズ シミュレータ・デバッガ ユーザーズマニュアル                          | ADJ - 702 - 355 |

| H8S、H8/300 シリーズ High-performance Embedded Workshop 3 チュートリアル    | RJJ10B0027      |

| H8S、H8/300 シリーズ High-performance Embedded Workshop 3 ユーザーズマニュアル | RJJ10B0029      |

### • アプリケーションノート

| 資料名                                        | 資料番号             |

|--------------------------------------------|------------------|

| H8S、H8/300 シリーズ C/C++コンパイラパッケージアプリケーションノート | RJJ05B0558       |

| 単一電源版 F-ZTAT マイコンオンボード書き込み                 | ADJ - 502 - 069A |

## 目次

| 1.  | 概要                         | 1-1  |

|-----|----------------------------|------|

| 1.1 | 特長                         | 1-1  |

| 1.2 |                            | 1-3  |

| 1.3 | ピン配置図                      |      |

| 1.4 | 端子機能                       |      |

| 2.  | CPU                        | 2-1  |

| 2.1 | アドレス空間とメモリマップ              | 2-2  |

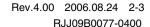

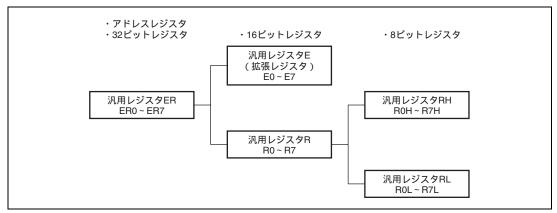

| 2.2 | レジスタ構成                     | 2-3  |

| 2.2 | 2.1 汎用レジスタ                 | 2-3  |

| 2.2 | 2.2 プログラムカウンタ(PC)          | 2-4  |

| 2.2 | 2.3 コンディションコードレジスタ ( CCR ) | 2-5  |

| 2.3 | データ形式                      | 2-6  |

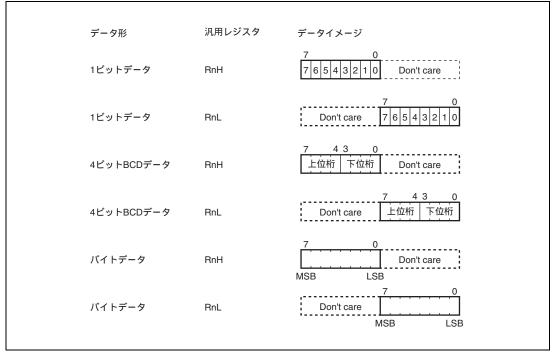

| 2.3 | 3.1 汎用レジスタのデータ形式           | 2-6  |

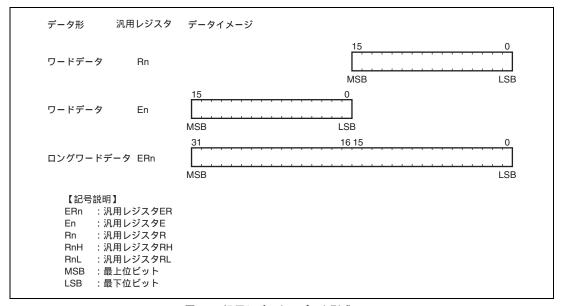

| 2.3 | 3.2 メモリ上のデータ形式             | 2-8  |

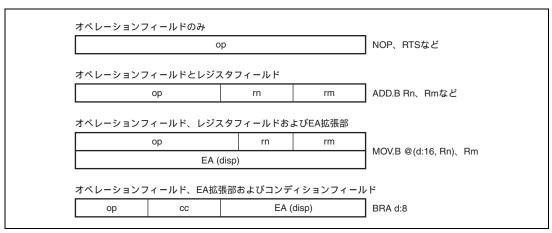

| 2.4 | 命令セット                      | 2-9  |

| 2.4 | 4.1 命令の機能別一覧               | 2-9  |

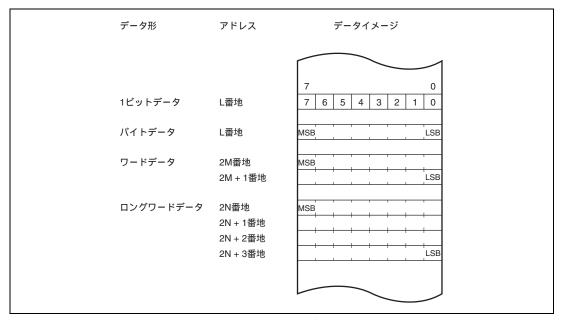

| 2.4 | 4.2 命令の基本フォーマット            | 2-17 |

| 2.5 | アドレッシングモードと実効アドレス          | 2-18 |

| 2.5 | 5.1 アドレッシングモード             | 2-18 |

| 2.5 | 5.2 実効アドレスの計算方法            | 2-21 |

| 2.6 | 基本バスサイクル                   | 2-23 |

| 2.6 | 6.1 内蔵メモリ(RAM、ROM)         | 2-23 |

| 2.6 | 6.2 内蔵周辺モジュール              | 2-24 |

| 2.7 | CPUの状態                     | 2-25 |

| 2.8 | 使用上の注意事項                   | 2-26 |

| 2.8 | 8.1 空きエリアへのデータアクセス         | 2-26 |

| 2.8 | 8.2 EEPMOV 命令              | 2-26 |

| 2.8 | 8.3 ビット操作命令                | 2-27 |

| 3.  | 例外処理                       | 3-1  |

| 3.1 | 例外処理要因とベクタアドレス             | 3-2  |

| 3.2 | リセット                       |      |

|     | 2.1 リセット例外処理               |      |

| 3.3       割り込み                                | 3-6  |

|-----------------------------------------------|------|

|                                               |      |

|                                               | 3-6  |

| 3.4.1 割り込み応答時間                                |      |

| 3.5 使用上の注意事項                                  | 3-7  |

| 3.5.1 スタック領域に関する使用上の注意事項                      | 3-7  |

| 3.5.2 ポートモードレジスタを書き換える際の注意事項                  | 3-8  |

| 3.5.3 割り込み要求フラグをクリアする方法                       | 3-10 |

| 4. 割り込みコントローラ                                 | 4-1  |

| 4.1 特長                                        | 4-1  |

| 4.2 入出力端子                                     | 4-2  |

| 4.3 レジスタの説明                                   | 4-2  |

| 4.3.1 割り込みエッジセレクトレジスタ (IEGR)                  | 4-3  |

| 4.3.2 ウェイクアップエッジセレクトレジスタ (WEGR)               | 4-4  |

| 4.3.3 割り込み許可レジスタ 1 (IENR1)                    | 4-5  |

| 4.3.4 割り込み許可レジスタ 2 (IENR2)                    | 4-6  |

| 4.3.5 割り込み要求レジスタ 1 (IRR1)                     | 4-7  |

| 4.3.6 割り込み要求レジスタ 2 (IRR2)                     | 4-8  |

| 4.3.7 ウェイクアップ割り込み要求レジスタ (IWPR)                | 4-9  |

| 4.3.8 インタラプトプライオリティレジスタ A ~ E ( IPRA ~ IPRE ) | 4-10 |

| 4.3.9 インタラプトマスクレジスタ ( INTM )                  | 4-11 |

| 4.4 割り込み要因                                    | 4-11 |

| 4.4.1 外部割り込み                                  | 4-11 |

| 4.4.2 内部割り込み                                  | 4-12 |

| 4.5 割り込み例外処理ベクタテーブル                           | 4-13 |

| 4.6 割り込み動作                                    | 4-15 |

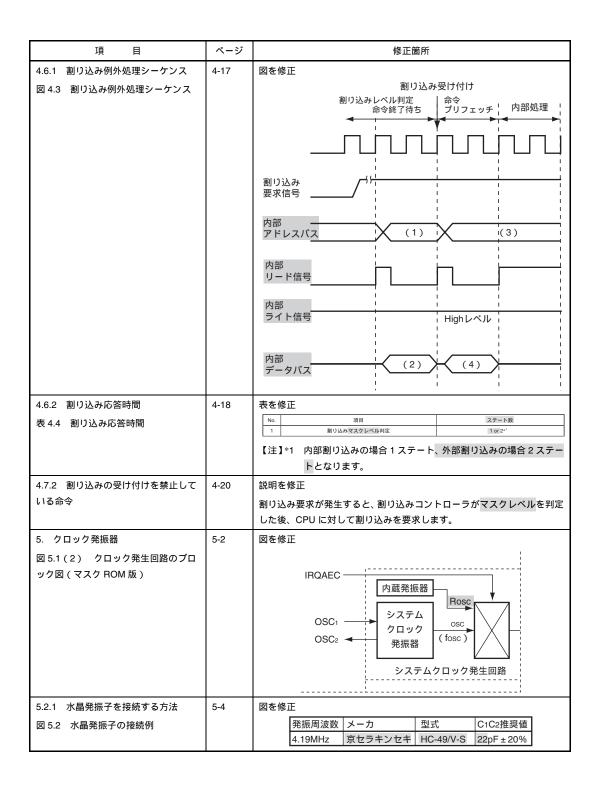

| 4.6.1 割り込み例外処理シーケンス                           | 4-16 |

| 4.6.2 割り込み応答時間                                | 4-18 |

| 4.7 使用上の注意事項                                  | 4-19 |

| 4.7.1 割り込みの発生とディスエーブルとの競合                     | 4-19 |

| 4.7.2 割り込みの受け付けを禁止している命令                      | 4-20 |

| 4.7.3 EEPMOV 命令実行中の割り込み                       | 4-20 |

| 4.7.4 IENR のクリアについて                           | 4-20 |

| 5. クロック発振器                                    | 5-1  |

| 5.1 レジスタの説明                                   | 5-3  |

| 5.1.1 サブ 32k コントロールレジスタ (SUB32CR)             | 5-3  |

| 5.1.2 発振器コントロールレジスタ(OSCCR)                    |      |

| 5.2 システムクロック発振器                               |      |

| 5.2.1 | 水晶発振子を接続する方法                              | 5-4  |

|-------|-------------------------------------------|------|

| 5.2.2 | セラミック発振子を接続する方法                           | 5-4  |

| 5.2.3 | 外部クロックを入力する方法                             | 5-5  |

| 5.2.4 | 内蔵発振器を選択する方法(マスク ROM 版のみ)                 | 5-5  |

| 5.3   | サブクロック発振器                                 | 5-6  |

| 5.3.1 | 32.768kHz/38.4kHz 水晶発振子を接続する方法            | 5-6  |

| 5.3.2 | サブクロックを必要としない場合の端子処理                      | 5-7  |

| 5.3.3 | 外部クロックを入力する方法                             | 5-7  |

| 5.4   | プリスケーラ                                    | 5-8  |

| 5.4.1 | プリスケーラ S                                  | 5-8  |

| 5.5   | 使用上の注意事項                                  | 5-8  |

| 5.5.1 | 発振子に関する注意事項                               | 5-8  |

| 5.5.2 | ボード設計上の注意事項                               | 5-10 |

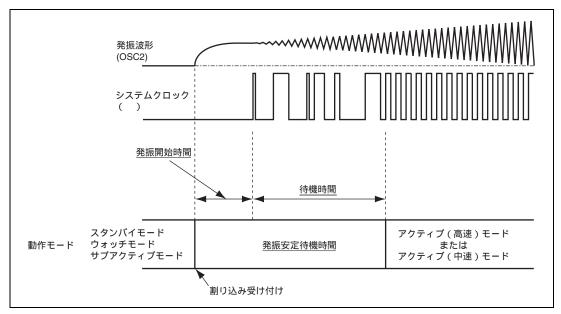

| 5.5.3 | 発振安定待機時間の定義                               | 5-10 |

| 5.5.4 | サプクロック停止状態に関する注意事項                        | 5-11 |

| 5.5.5 | 発振子をご使用の場合の注意事項                           | 5-12 |

| 5.5.6 | パワーオンリセット回路使用時の注意事項                       | 5-12 |

| 6. 低; | 肖費電力モード                                   | 6-1  |

| 6.1   | レジスタの説明                                   | 6-2  |

| 6.1.1 | システムコントロールレジスタ 1 ( SYSCR1 )               | 6-2  |

| 6.1.2 | システムコントロールレジスタ 2 ( SYSCR2 )               | 6-3  |

| 6.1.3 | クロック停止レジスタ 1、2 ( CKSTPR1、 CKSTPR2 )       | 6-4  |

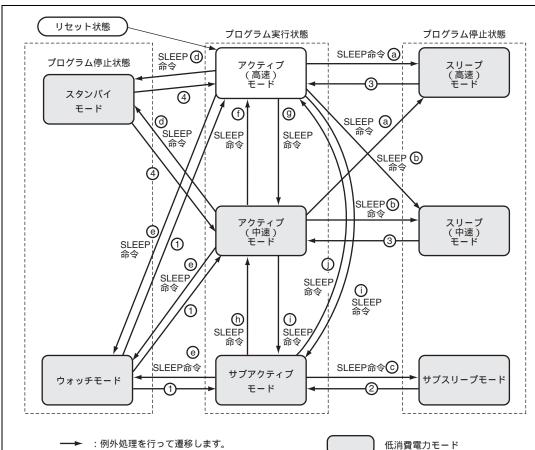

| 6.2   | モード間遷移とLSIの状態                             | 6-5  |

| 6.2.1 | スリープモード                                   | 6-9  |

| 6.2.2 | スタンパイモード                                  | 6-9  |

| 6.2.3 | ウォッチモード                                   | 6-10 |

| 6.2.4 | サブスリープモード                                 | 6-10 |

| 6.2.5 | サブアクティブモード                                | 6-11 |

| 6.2.6 | アクティブ ( 中速 ) モード                          | 6-11 |

| 6.3   | 直接遷移                                      | 6-12 |

| 6.3.1 | アクティブ(高速)モードからアクティブ(中速)モードへの直接遷移時の時間について、 | 6-13 |

| 6.3.2 | アクティブ(高速)モードからサブアクティブモードへの直接遷移時の時間について    | 6-13 |

| 6.3.3 | アクティブ(中速)モードからアクティブ(高速)モードへの直接遷移時の時間について、 | 6-13 |

| 6.3.4 | アクティブ(中速)モードからサブアクティブモードへの直接遷移時の時間について    | 6-14 |

| 6.3.5 | サブアクティブモードからアクティブ(高速)モードへの直接遷移時の時間について    | 6-14 |

| 6.3.6 | サブアクティブモードからアクティブ(中速)モードへの直接遷移時の時間について    | 6-15 |

| 6.3.7 | 直接遷移前後で外部入力信号が変化する場合の注意事項                 | 6-15 |

| 6.4   | モジュールスタンバイ機能                              | 6-16 |

| 6.5   | 使用上の注意事項                                  | 6-16 |

| 6.5.1  | スタンバイモードへの遷移と端子状態             | 6-16 |

|--------|-------------------------------|------|

| 6.5.2  | スタンパイモード前後で外部入力信号が変化する場合の注意事項 | 6-16 |

| 7. RO  | DM                            | 7-1  |

| 7.1    | ブロック構成                        | 7-2  |

| 7.2    | レジスタの説明                       | 7-3  |

| 7.2.1  | フラッシュメモリコントロールレジスタ 1(FLMCR1)  | 7-3  |

| 7.2.2  | フラッシュメモリコントロールレジスタ 2(FLMCR2)  | 7-4  |

| 7.2.3  | ブロック指定レジスタ 1 (EBR1)           | 7-4  |

| 7.2.4  | フラッシュメモリパワーコントロールレジスタ(FLPWCR) | 7-5  |

| 7.2.5  | フラッシュメモリイネーブルレジスタ(FENR )      | 7-5  |

| 7.3    | オンボードプログラミング                  | 7-6  |

| 7.3.1  | プートモード                        | 7-6  |

| 7.3.2  | ユーザモードでの書き込み / 消去             | 7-9  |

| 7.4    | 書き込み/消去プログラム                  | 7-10 |

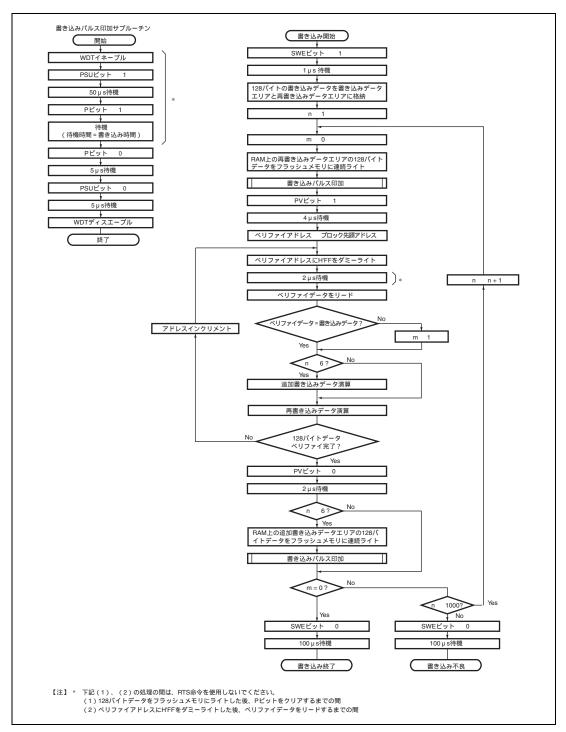

| 7.4.1  | プログラム / プログラムベリファイ            | 7-10 |

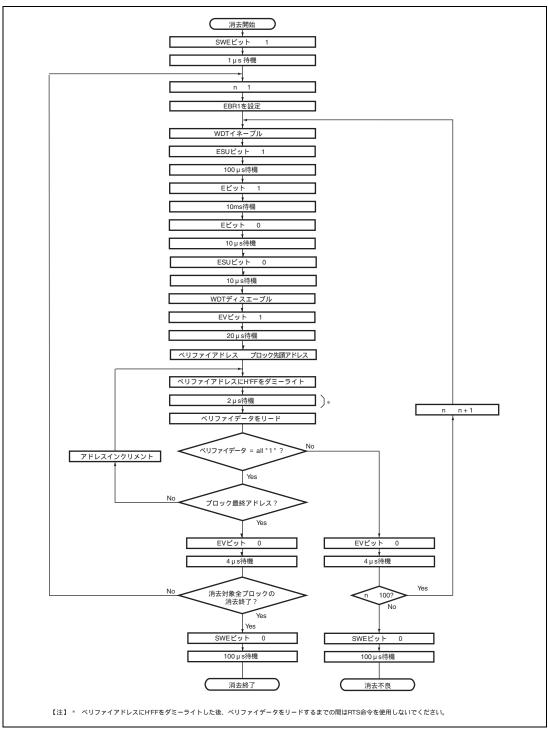

| 7.4.2  | イレース / イレースベリファイ              | 7-13 |

| 7.4.3  | フラッシュメモリの書き込み/消去時の割り込み        | 7-13 |

| 7.5    | 書き込み / 消去プロテクト                | 7-15 |

| 7.5.1  | ハードウェアプロテクト                   | 7-15 |

| 7.5.2  | ソフトウェアプロテクト                   | 7-15 |

| 7.5.3  | エラープロテクト                      | 7-15 |

| 7.6    | ライタモード                        | 7-16 |

| 7.7    | フラッシュメモリの低消費電力動作              | 7-16 |

| 7.8    | モジュールスタンパイモード設定時の注意事項         | 7-17 |

| 8. RA  | M                             | 8-1  |

| 9. I/O | ポート                           | 9-1  |

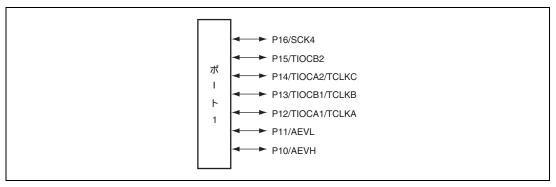

| 9.1    | ポート1                          | 9-1  |

| 9.1.1  | ポートデータレジスタ 1 ( PDR1 )         | 9-2  |

| 9.1.2  | ポートコントロールレジスタ 1(PCR1)         | 9-2  |

| 9.1.3  | ポートプルアップコントロールレジスタ 1(PUCR1)   | 9-2  |

| 9.1.4  | ポートモードレジスタ 1(PMR1)            | 9-3  |

| 9.1.5  | 端子機能                          | 9-3  |

| 9.1.6  | 入力プルアップ MOS                   | 9-6  |

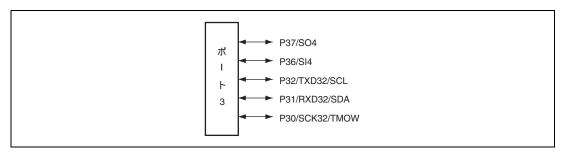

| 9.2    | ポート3                          | 9-7  |

| 9.2.1  | ポートデータレジスタ 3 ( PDR3 )         | 9-7  |

| 9.2.2  | ポートコントロールレジスタ 3(PCR3)         | 9-8  |

| 9.2.3  | ポートプルアップコントロールレジスタ 3(PUCR3)   | 9-8  |

| 9.2.4  | ポートモードレジスタ3(PMR3)              | 9-8  |

|--------|--------------------------------|------|

| 9.2.5  | 端子機能                           | 9-9  |

| 9.2.6  | 入力プルアップ MOS                    | 9-10 |

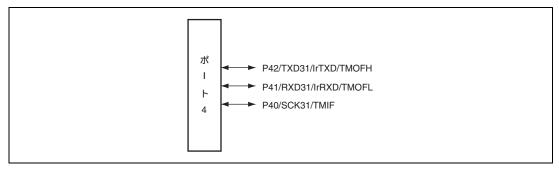

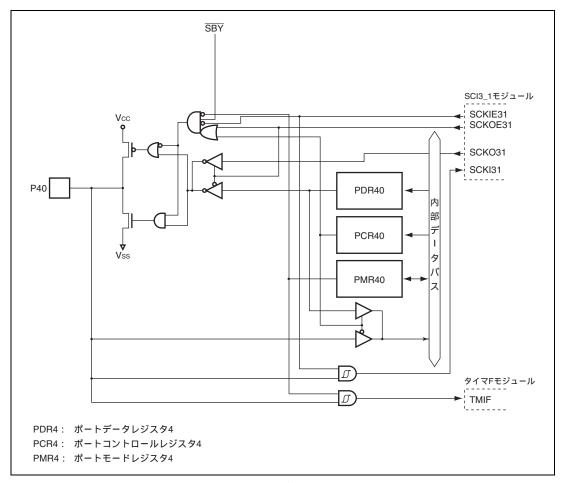

| 9.3    | ポート4                           | 9-11 |

| 9.3.1  | ポートデータレジスタ 4 ( PDR4 )          | 9-11 |

| 9.3.2  | ポートコントロールレジスタ 4(PCR4)          | 9-12 |

| 9.3.3  | ポートモードレジスタ4(PMR4)              | 9-12 |

| 9.3.4  | 端子機能                           | 9-13 |

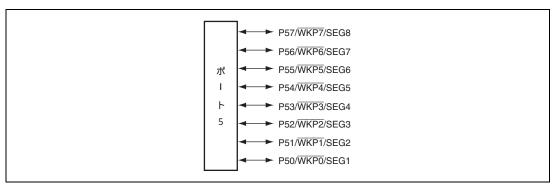

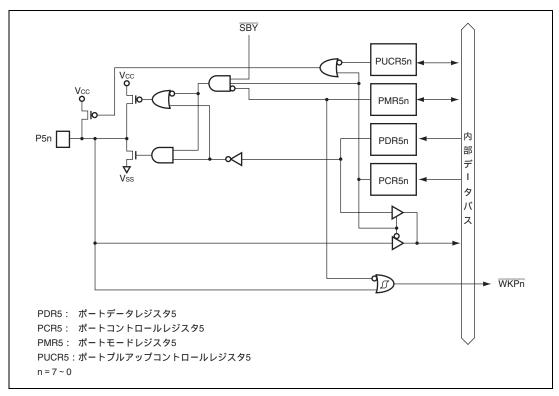

| 9.4    | ポート5                           | 9-14 |

| 9.4.1  | ポートデータレジスタ 5 ( PDR5 )          | 9-14 |

| 9.4.2  | ポートコントロールレジスタ 5 ( PCR5 )       | 9-15 |

| 9.4.3  | ポートプルアップコントロールレジスタ 5(PUCR5)    | 9-15 |

| 9.4.4  | ポートモードレジスタ5(PMR5)              | 9-15 |

| 9.4.5  | 端子機能                           | 9-16 |

| 9.4.6  | 入力プルアップ MOS                    | 9-16 |

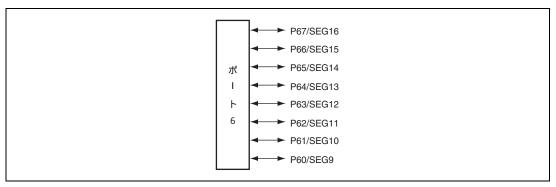

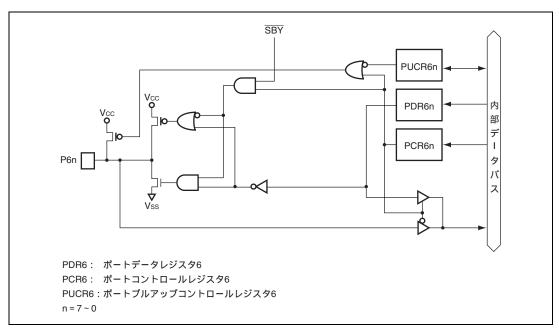

| 9.5    | ポート6                           | 9-17 |

| 9.5.1  | ポートデータレジスタ 6 ( PDR6 )          | 9-17 |

| 9.5.2  | ポートコントロールレジスタ 6 ( PCR6 )       | 9-18 |

| 9.5.3  | ポートプルアップコントロールレジスタ 6 ( PUCR6 ) | 9-18 |

| 9.5.4  | 端子機能                           | 9-19 |

| 9.5.5  | 入力プルアップ MOS                    | 9-19 |

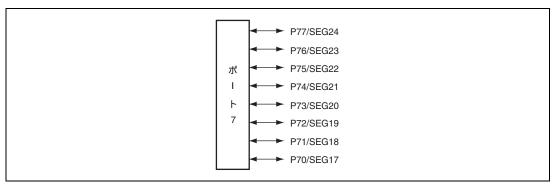

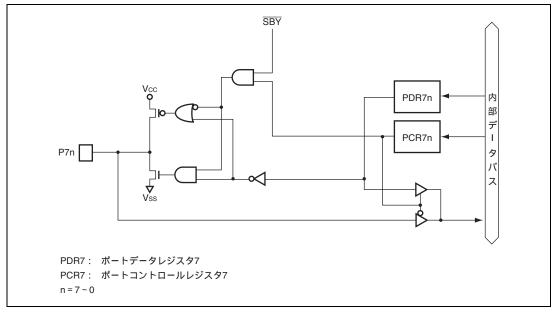

| 9.6    | ポート7                           | 9-20 |

| 9.6.1  | ポートデータレジスタ7(PDR7)              | 9-20 |

| 9.6.2  | ポートコントロールレジスタ 7 ( PCR7 )       | 9-21 |

| 9.6.3  | 端子機能                           | 9-21 |

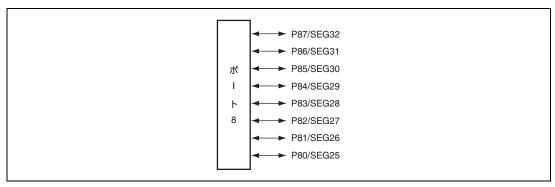

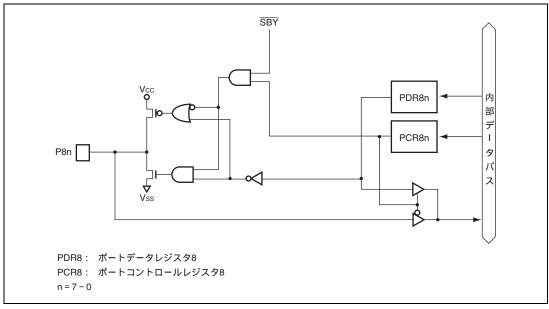

| 9.7    | ポート8                           | 9-22 |

| 9.7.1  | ポートデータレジスタ8(PDR8)              | 9-22 |

| 9.7.2  | ポートコントロールレジスタ 8 ( PCR8 )       | 9-23 |

| 9.7.3  | 端子機能                           | 9-23 |

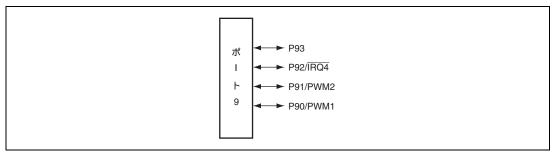

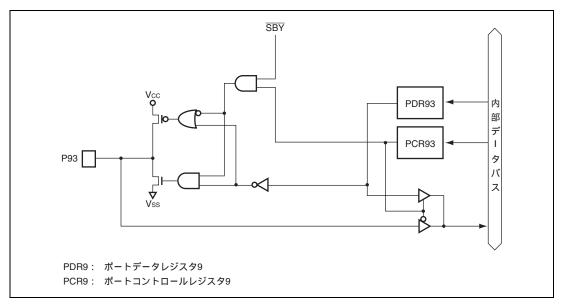

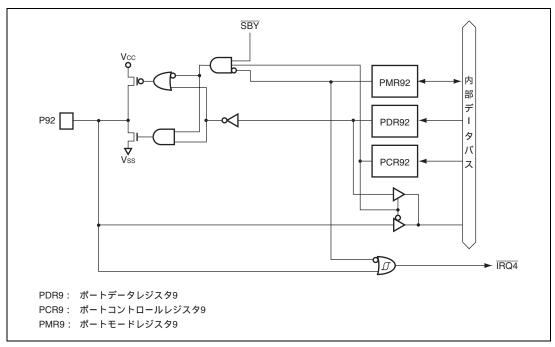

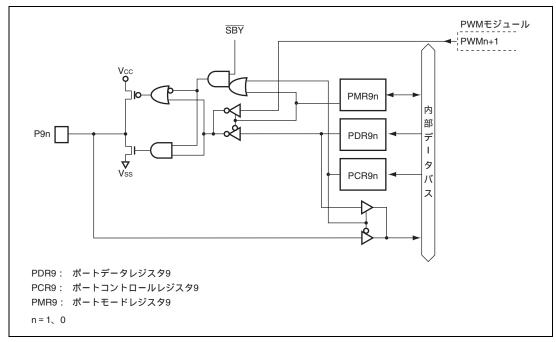

| 9.8    | ポート9                           | 9-24 |

| 9.8.1  | ポートデータレジスタ9(PDR9)              |      |

| 9.8.2  | ポートコントロールレジスタ 9 ( PCR9 )       | 9-25 |

| 9.8.3  | ポートモードレジスタ9(PMR9)              | 9-25 |

| 9.8.4  | 端子機能                           | 9-26 |

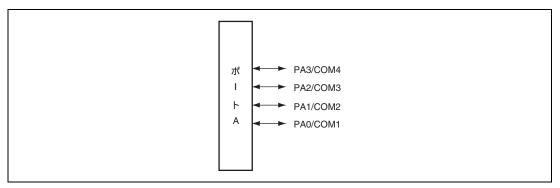

| 9.9    | ポートA                           |      |

| 9.9.1  | ポートデータレジスタ A(PDRA)             |      |

| 9.9.2  | ポートコントロールレジスタ A(PCRA)          |      |

| 9.9.3  | 端子機能                           | 9-28 |

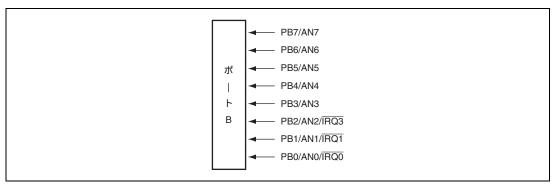

| 9.10   | ポートB                           |      |

| 9.10.1 | ポートデータレジスタ B ( PDRB )          | 9-30 |

| 9.10.2 | ポートモードレジスタ B(PMRB)             | 9-31 |

| 9.10.3 | 端子機能                                   |       |

|--------|----------------------------------------|-------|

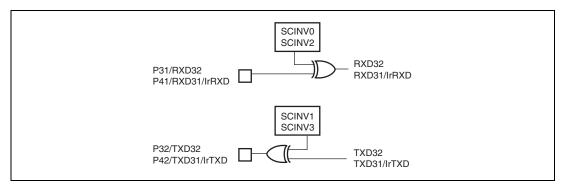

| 9.11   | 入出力データの反転                              |       |

| 9.11.1 | シリアルポートコントロールレジスタ(SPCR)                | 9-34  |

| 9.12   | 使用上の注意事項                               | 9-36  |

| 9.12.1 | 未使用端子の処理                               | 9-36  |

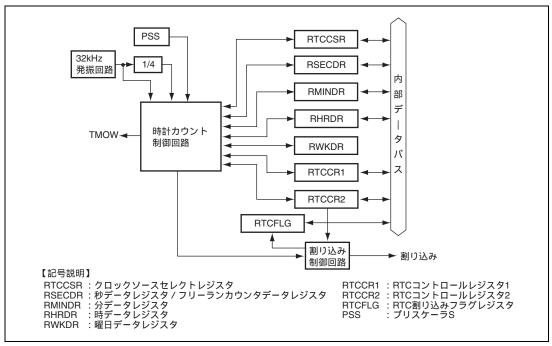

| 10. リア | 'ルタイムクロック(RTC)                         | 10-1  |

| 10.1   | 特長                                     | 10-1  |

| 10.2   | 入出力端子                                  | 10-2  |

| 10.3   | レジスタの説明                                | 10-2  |

| 10.3.1 | 秒データレジスタ / フリーランカウンタデータレジスタ ( RSECDR ) | 10-2  |

| 10.3.2 | 分データレジスタ(RMINDR)                       | 10-3  |

| 10.3.3 | 時データレジスタ(RHRDR)                        | 10-3  |

| 10.3.4 | 曜日データレジスタ(RWKDR)                       | 10-4  |

| 10.3.5 | RTC コントロールレジスタ1 (RTCCR1)               | 10-5  |

| 10.3.6 | RTC コントロールレジスタ 2 (RTCCR2)              | 10-6  |

| 10.3.7 | クロックソースセレクトレジスタ(RTCCSR)                | 10-7  |

| 10.3.8 | RTC 割り込みフラグレジスタ(RTCFLG)                | 10-8  |

| 10.4   | RTCの動作                                 | 10-9  |

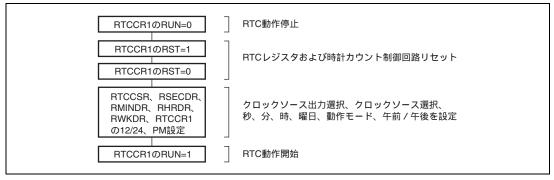

| 10.4.1 | 電源投入後のレジスタの初期設定                        |       |

| 10.4.2 | 初期設定手順                                 | 10-9  |

| 10.4.3 | 時刻読み出し手順                               | 10-9  |

| 10.5   | 割り込み要因                                 | 10-10 |

| 10.6   | 使用上の注意事項                               | 10-11 |

| 10.6.1 | 時計カウントに関する注意事項                         | 10-11 |

| 10.6.2 | 割り込みを使用する場合の注意事項                       |       |

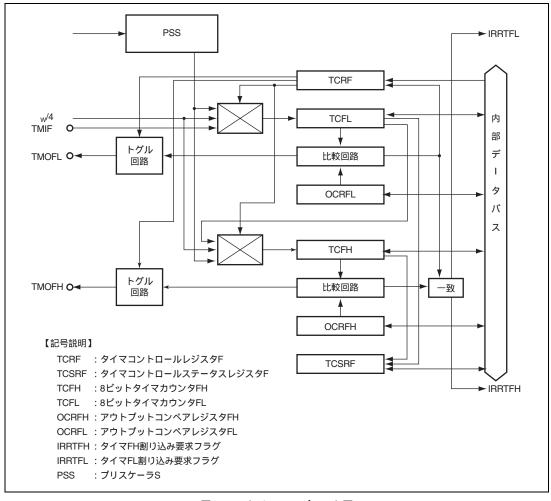

| 11. タイ | マF                                     | 11-1  |

| 11.1   | 特長                                     | 11-1  |

| 11.2   | 入出力端子                                  |       |

| 11.3   | レジスタの説明                                | 11-3  |

| 11.3.1 |                                        |       |

| 11.3.2 | アウトプットコンペアレジスタ FH、FL(OCRFH、OCRFL)      |       |

| 11.3.3 | タイマコントロールレジスタ F ( TCRF )               |       |

| 11.3.4 | タイマコントロールステータスレジスタ F ( TCSRF )         |       |

| 11.3.4 | 動作説明                                   |       |

| 11.4.1 | #// F の動作                              |       |

| 11.4.1 | TCF のカウントタイミング                         |       |

| 11.4.2 | TMOFH、TMOFL 出力タイミング                    |       |

| 11.4.3 | TCF のクリアタイミング                          |       |

| 11.4.4 | 101 0// 3/ / 1 ~ / /                   | 11-9  |

| 11.4.5   | タイマオーバフローフラグ ( OVF ) のセットタイミング | 11-9  |

|----------|--------------------------------|-------|

| 11.4.6   | コンペアマッチフラグのセットタイミング            | 11-9  |

| 11.5     | タイマFの動作モード                     | 11-10 |

| 11.6     | 使用上の注意事項                       | 11-10 |

| 11.6.1   | 16 ビットタイマモード                   | 11-10 |

| 11.6.2   | 8 ビットタイマモード                    | 11-11 |

| 11.6.3   | 各フラグのクリア                       | 11-11 |

| 11.6.4   | タイマカウンタ ( TCF ) のリード / ライト     | 11-13 |

| 12. 16 l | ビットタイマパルスユニット(TPU)             | 12-1  |

| 12.1     | 特長                             | 12-1  |

| 12.2     | 入出力端子                          | 12-3  |

| 12.3     | レジスタの説明                        | 12-4  |

| 12.3.1   | タイマコントロールレジスタ(TCR)             | 12-5  |

| 12.3.2   | タイマモードレジスタ(TMDR)               | 12-7  |

| 12.3.3   | タイマ I/O コントロールレジスタ ( TIOR )    | 12-7  |

| 12.3.4   | タイマインタラプトイネーブルレジスタ(TIER)       | 12-11 |

| 12.3.5   | タイマステータスレジスタ(TSR)              | 12-12 |

| 12.3.6   | タイマカウンタ ( TCNT )               | 12-13 |

| 12.3.7   | タイマジェネラルレジスタ(TGR)              | 12-13 |

| 12.3.8   | タイマスタートレジスタ ( TSTR )           | 12-13 |

| 12.3.9   | タイマシンクロレジスタ ( TSYR )           | 12-14 |

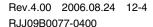

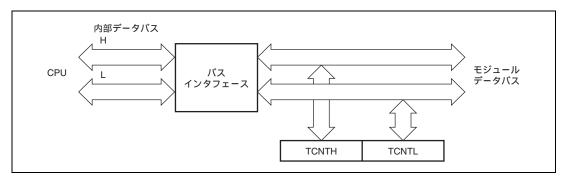

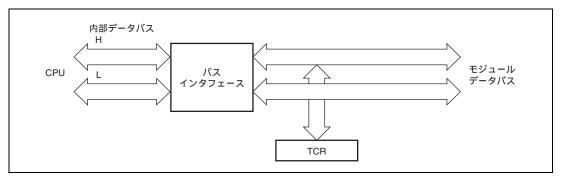

| 12.4     | CPUとのインタフェース                   | 12-14 |

| 12.4.1   | 16 ビットレジスタ                     | 12-14 |

| 12.4.2   | 8 ビットレジスタ                      | 12-15 |

| 12.5     | 動作説明                           | 12-16 |

| 12.5.1   | 基本動作                           | 12-16 |

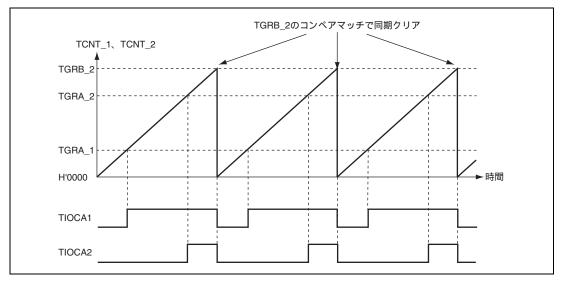

| 12.5.2   | 同期動作                           | 12-21 |

| 12.5.3   | カスケード接続動作                      | 12-22 |

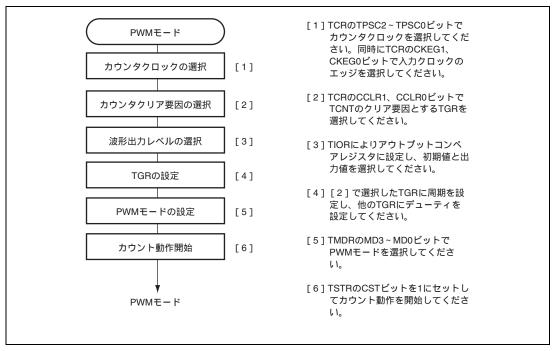

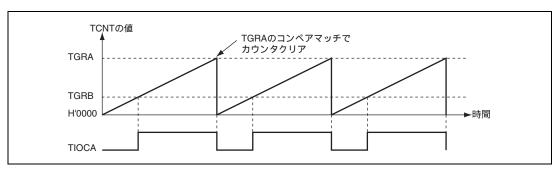

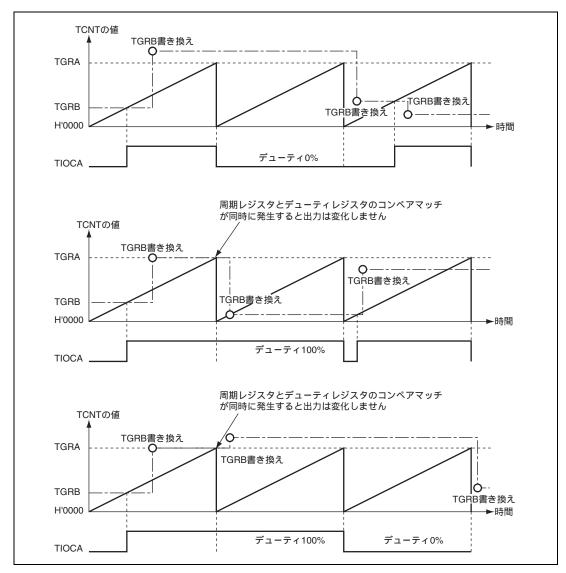

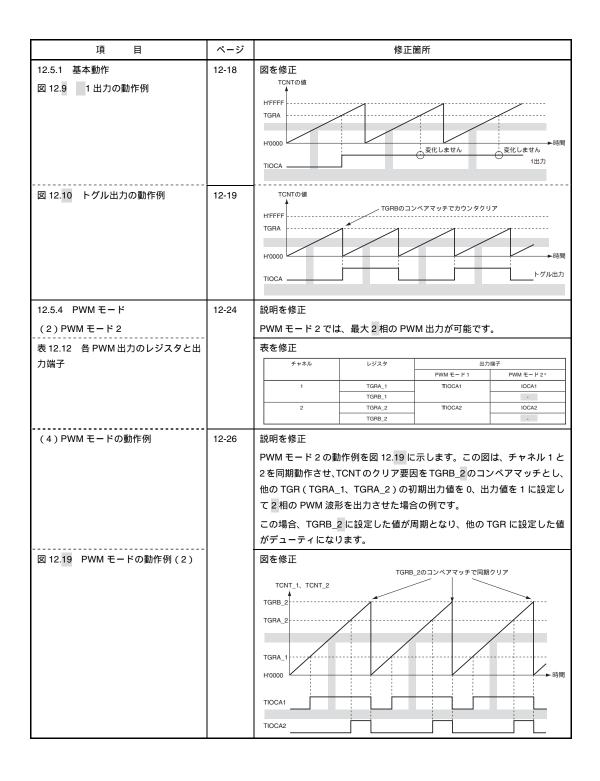

| 12.5.4   | PWM モード                        | 12-24 |

| 12.6     | 割り込み要因                         | 12-28 |

| 12.7     | 動作タイミング                        | 12-29 |

| 12.7.1   | 入出力タイミング                       | 12-29 |

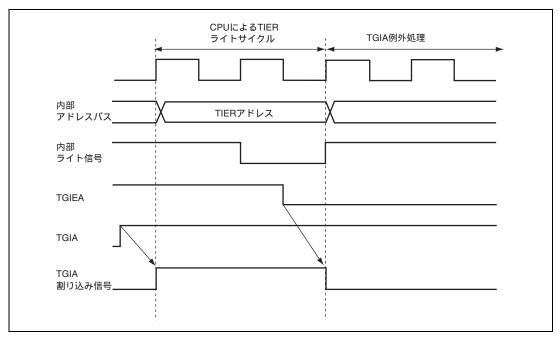

| 12.7.2   | 割り込み信号タイミング                    | 12-32 |

| 12.8     | 使用上の注意事項                       | 12-34 |

| 12.8.1   | モジュールスタンバイ機能の設定                | 12-34 |

| 12.8.2   | 入力クロックの制限事項                    | 12-34 |

| 12.8.3   | 周期設定上の注意事項                     | 12-34 |

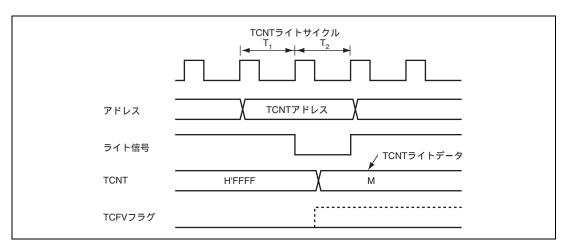

| 12.8.4   | TCNT のライトとクリアの競合               | 12-35 |

| 12.8.5   | TCNT のライトとカウントアップの競合           | 12-35 |

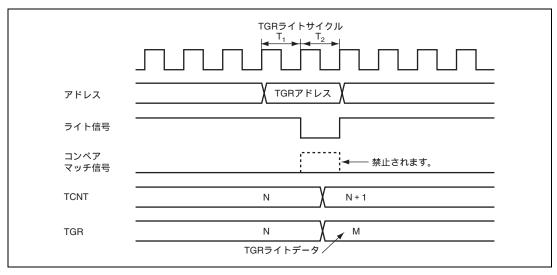

| 12.8.6 | TGR のライトとコンペアマッチの競合                   | 12-36 |

|--------|---------------------------------------|-------|

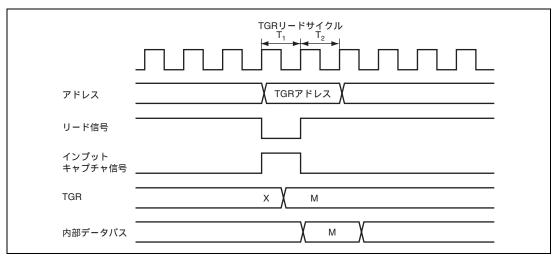

| 12.8.7 | TGR のリードとインプットキャプチャの競合                | 12-37 |

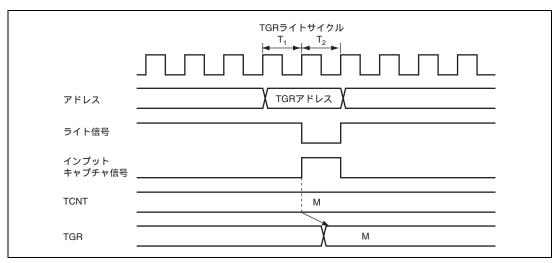

| 12.8.8 | TGR のライトとインプットキャプチャの競合                | 12-37 |

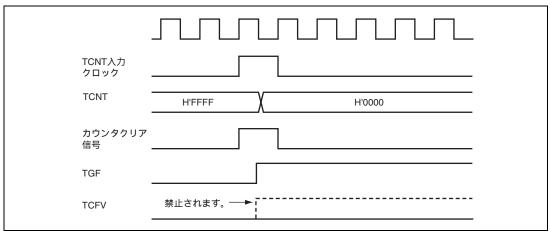

| 12.8.9 | オーバフローとカウンタクリアの競合                     | 12-38 |

| 12.8.1 | 0 TCNT のライトとオーバフローの競合                 | 12-38 |

| 12.8.1 | 1 入出力端子の兼用                            | 12-39 |

| 12.8.1 | 2 モジュールスタンバイ時の割り込み                    | 12-39 |

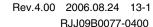

| 13. 非同 | 引期イベントカウンタ(AEC)                       | 13-1  |

| 13.1   | 特長                                    | 13-1  |

| 13.2   | 入出力端子                                 | 13-2  |

| 13.3   | レジスタの説明                               | 13-3  |

| 13.3.1 | イベントカウンタ PWM コンペアレジスタ(ECPWCR)         | 13-3  |

| 13.3.2 | イベントカウンタ PWM データレジスタ(ECPWDR)          | 13-4  |

| 13.3.3 | 入力端子エッジセレクトレジスタ(AEGSR )               | 13-4  |

| 13.3.4 | イベントカウンタコントロールレジスタ(ECCR)              | 13-5  |

| 13.3.5 | イベントカウンタコントロール / ステータスレジスタ(ECCSR )    | 13-6  |

| 13.3.6 | イベントカウンタ H ( ECH )                    | 13-7  |

| 13.3.7 | イベントカウンタ L ( ECL )                    | 13-7  |

| 13.4   | 動作説明                                  | 13-8  |

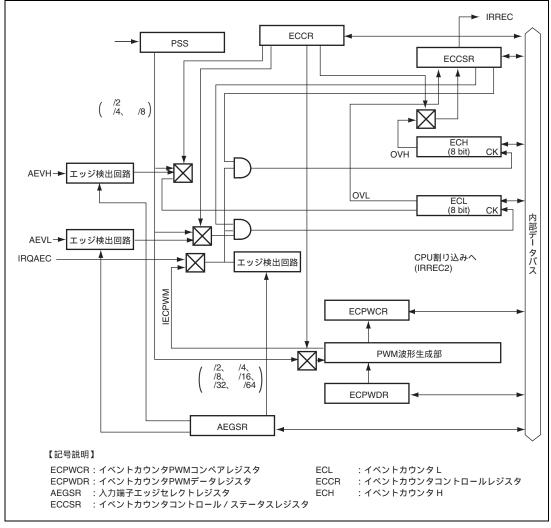

| 13.4.1 | 16 ビットカウンタの動作                         | 13-8  |

| 13.4.2 | 8 ビットカウンタの動作                          | 13-9  |

| 13.4.3 | IRQAEC の動作                            | 13-10 |

| 13.4.4 | イベントカウンタ PWM の動作                      | 13-10 |

| 13.4.5 | クロック入力許可 / 禁止機能の動作                    | 13-11 |

| 13.5   | 非同期イベントカウンタの動作モード                     | 13-12 |

| 13.6   | 使用上の注意事項                              | 13-13 |

| 14. ウォ | ォッチドッグタイマ                             | 14-1  |

| 14.1   | 特長                                    | 14-1  |

| 14.2   | レジスタの説明                               | 14-2  |

| 14.2.1 | タイマコントロール / ステータスレジスタ WD1 ( TCSRWD1 ) | 14-3  |

| 14.2.2 |                                       |       |

| 14.2.3 |                                       |       |

| 14.2.4 | タイマモードレジスタ WD ( TMWD )                | 14-5  |

| 14.3   | 動作説明                                  |       |

| 14.3.1 | ウォッチドッグタイマ時の動作                        | 14-6  |

| 14.3.2 |                                       |       |

| 14.3.3 | オーバフローフラグ(OVF)セットタイミング                | 14-7  |

| 14.4   | 割り込み                                  | 14-8  |

| 14.5    | 使用上の注意事項                         | 14-8  |

|---------|----------------------------------|-------|

| 14.5.1  | ウォッチドッグタイマモードとインターバルタイマモードの切り替え  | 14-8  |

| 14.5.2  | モジュールスタンバイモード制御                  | 14-8  |

| 15. シリ  | アルコミュニケーションインタフェース 3(SCI3、IrDA)  | 15-1  |

| 15.1    | 特長                               | 15-1  |

| 15.2    | 入出力端子                            | 15-5  |

| 15.3    | レジスタの説明                          | 15-5  |

| 15.3.1  | レシープシフトレジスタ ( RSR )              | 15-5  |

| 15.3.2  | レシープデータレジスタ ( RDR )              | 15-5  |

| 15.3.3  | トランスミットシフトレジスタ(TSR)              | 15-6  |

| 15.3.4  | トランスミットデータレジスタ(TDR)              | 15-6  |

| 15.3.5  | シリアルモードレジスタ ( SMR )              | 15-6  |

| 15.3.6  | シリアルコントロールレジスタ ( SCR )           | 15-8  |

| 15.3.7  | シリアルステータスレジスタ ( SSR )            | 15-10 |

| 15.3.8  | ビットレートレジスタ ( BRR )               | 15-12 |

| 15.3.9  | シリアルポートコントロールレジスタ(SPCR)          | 15-19 |

| 15.3.10 | IrDA コントロールレジスタ(IrCR)            | 15-20 |

| 15.4    | 調歩同期式モードの動作説明                    | 15-21 |

| 15.4.1  | クロック                             | 15-21 |

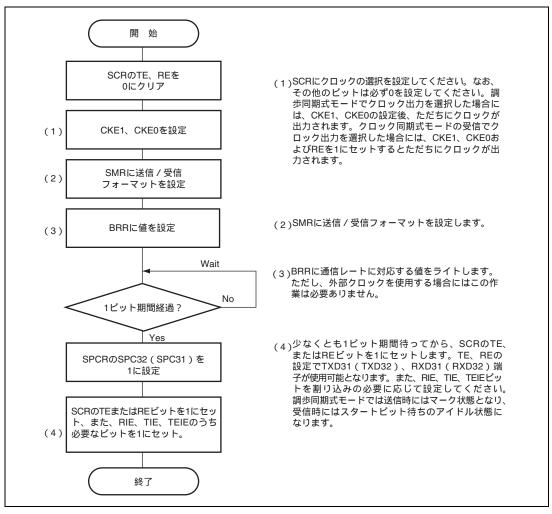

| 15.4.2  | SCI3 の初期化                        | 15-24 |

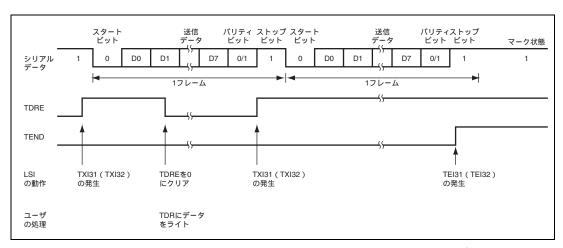

| 15.4.3  | データ送信                            | 15-25 |

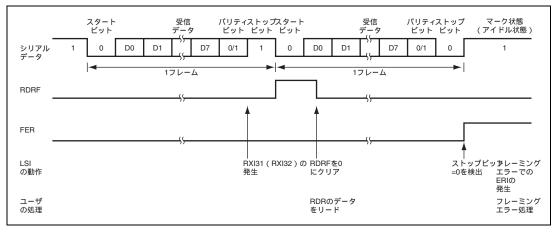

| 15.4.4  | データ受信                            | 15-27 |

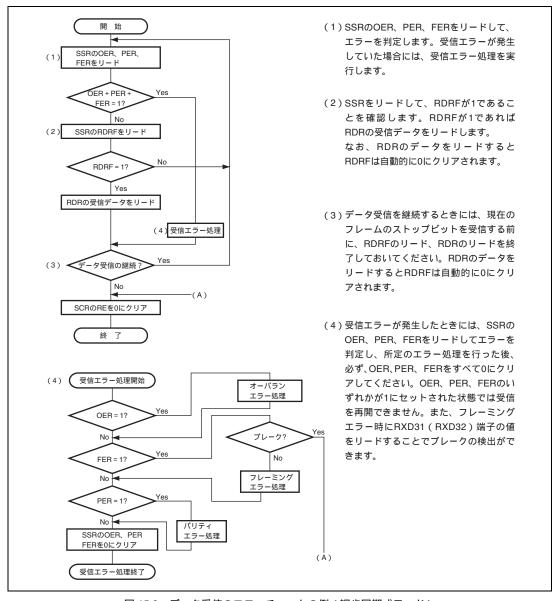

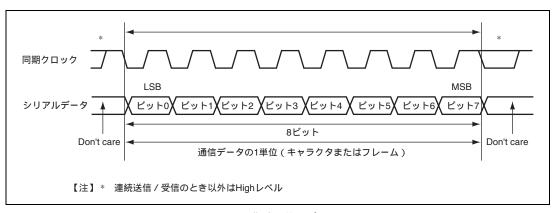

| 15.5    | クロック同期式モードの動作説明                  | 15-30 |

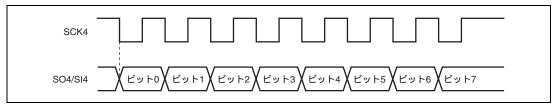

| 15.5.1  | クロック                             | 15-30 |

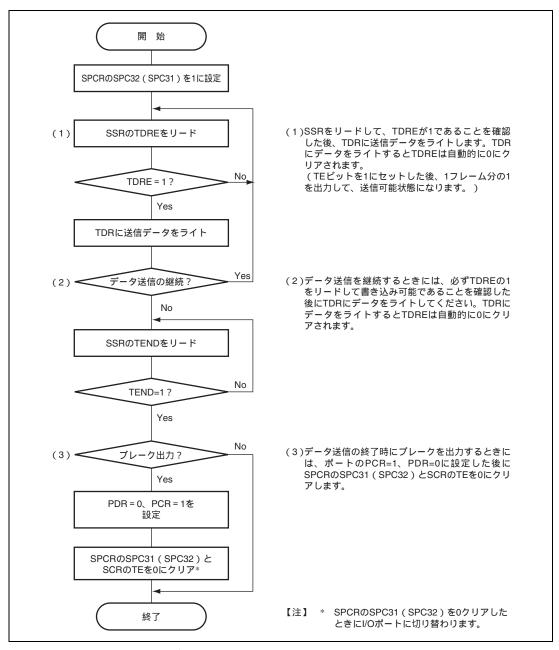

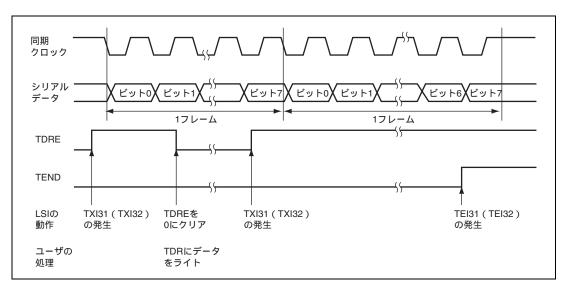

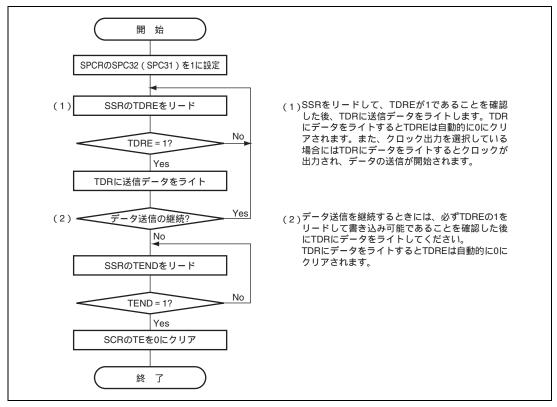

| 15.5.2  | SCI3 の初期化                        | 15-30 |

| 15.5.3  | データ送信                            | 15-31 |

| 15.5.4  | データ受信                            | 15-33 |

| 15.5.5  | データ送受信同時動作                       | 15-35 |

| 15.6    | IrDA動作                           | 15-36 |

| 15.6.1  | 送信                               | 15-37 |

| 15.6.2  | 受信                               | 15-38 |

| 15.6.3  | High パルス幅の選択                     | 15-38 |

| 15.7    | 割り込み要求                           | 15-39 |

| 15.8    | 使用上の注意事項                         | 15-42 |

| 15.8.1  | ブレークの検出と処理について                   | 15-42 |

| 15.8.2  | マーク状態とブレークの送出                    |       |

| 15.8.3  | 受信エラーフラグと送信動作について(クロック同期式モードのみ)  | 15-42 |

| 15.8.4  | 調歩同期式モードの受信データサンプリングタイミングと受信マージン | 15-42 |

| 15.8.5  | SCK31 (SCK32)端子機能切り替えに伴う注意事項     | 15-43 |

| 15.8.6   | TDR へのライトと TDRE の関係について                                    | 15-44 |

|----------|------------------------------------------------------------|-------|

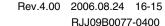

| 15.8.7   | RDR のリードと RDRF の関係について                                     | 15-44 |

| 15.8.8   | 状態遷移時における送信および受信動作について                                     | 15-45 |

| 15.8.9   | サブアクティブモード、サブスリープモード時の設定について                               | 15-45 |

| 15.8.10  | シリアルコミュニケーションインタフェース 3 を実行する際に使用する発振器について<br>(マスク ROM 版のみ) | 15-45 |

| 16. シリ   | Jアルコミュニケーションインタフェース 4(SCI4)                                | 16-1  |

| 16.1     | 特長                                                         |       |

| 16.2     | 入出力端子                                                      |       |

| 16.3     | レジスタの説明                                                    |       |

| 16.3.1   | シリアルコントロールレジスタ 4(SCR4)                                     |       |

| 16.3.2   | シリアルコントロールステータスレジスタ 4(SCSR4)                               |       |

| 16.3.3   | トランスミットデータレジスタ 4(TDR4)                                     |       |

| 16.3.4   | レシープデータレジスタ 4(RDR4)                                        |       |

| 16.3.5   | シフトレジスタ 4(SR4)                                             | 16-7  |

| 16.4     | 動作説明                                                       | 16-8  |

| 16.4.1   | クロック                                                       |       |

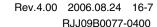

| 16.4.2   | データ転送フォーマット                                                | 16-8  |

| 16.4.3   | データの送信 / 受信動作                                              | 16-9  |

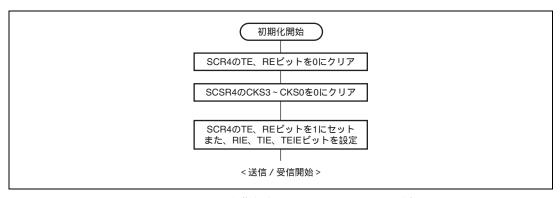

| 16.4.4   | データ送信                                                      | 16-10 |

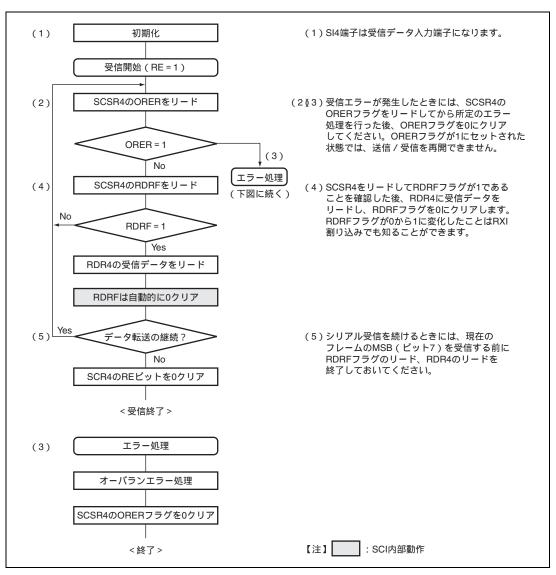

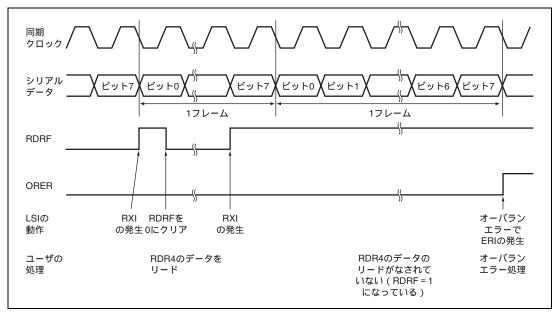

| 16.4.5   | データ受信                                                      | 16-12 |

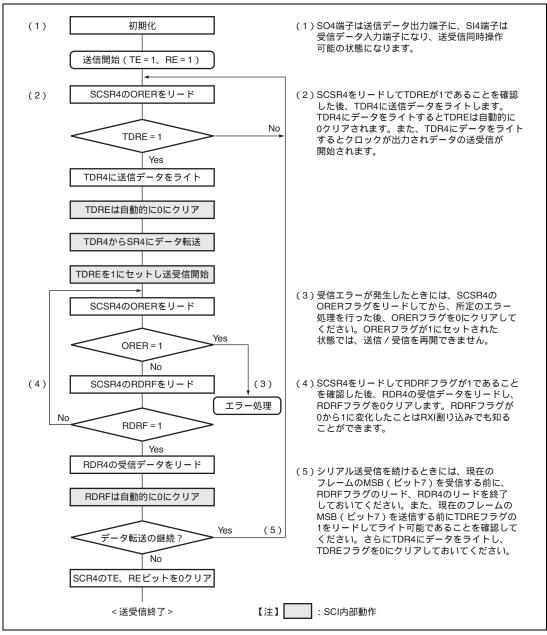

| 16.4.6   | データ送受信同時動作                                                 | 16-14 |

| 16.5     | 割り込み要因                                                     | 16-15 |

| 16.6     | 使用上の注意事項                                                   | 16-16 |

| 16.6.1   | TDR4 へのライトと TDRE の関係について                                   | 16-16 |

| 16.6.2   | 受信エラーフラグと送信動作について                                          | 16-16 |

| 16.6.3   | RDR4 のリードと RDRF の関係について                                    | 16-16 |

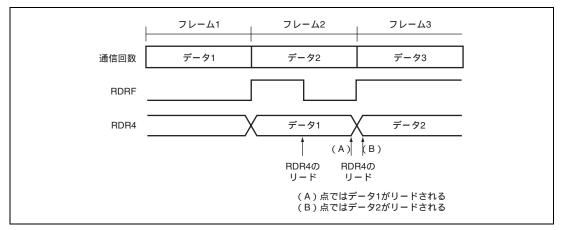

| 16.6.4   | 内部クロック /2 選択時の SCK4 出力波形について                               | 16-17 |

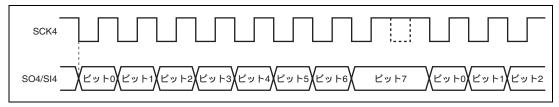

| 17. 14 l | ビット PWM                                                    | 17-1  |

| 17.1     | 特長                                                         | 17-1  |

| 17.2     | 入出力端子                                                      | 17-2  |

| 17.3     | レジスタの説明                                                    | 17-2  |

| 17.3.1   | PWM コントロールレジスタ ( PWCR )                                    | 17-2  |

| 17.3.2   | PWM データレジスタ(PWDR)                                          | 17-3  |

| 17.4     | 動作説明                                                       | 17-3  |

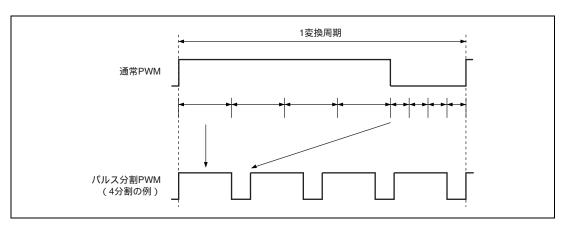

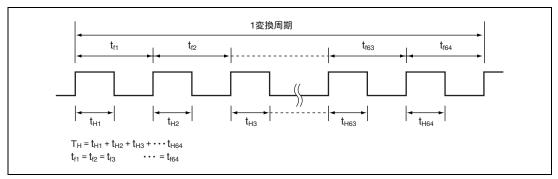

| 17.4.1   | パルス分割 PWM の原理                                              | 17-3  |

| 17.4.2   | パルス分割 PWM の設定手順                                            | 17-3  |

| 17.4.3   | パルス分割 PWM の動作説明                                            | 17-4  |

| 17.4.4  | 標準 PWM の動作設定                   | 17-4  |

|---------|--------------------------------|-------|

| 17.5    | PWMの動作モード                      | 17-5  |

| 17.6    | 使用上の注意事項                       | 17-5  |

| 17.6.1  | PWDR のライトと PWM 波形への反映タイミングについて | 17-5  |

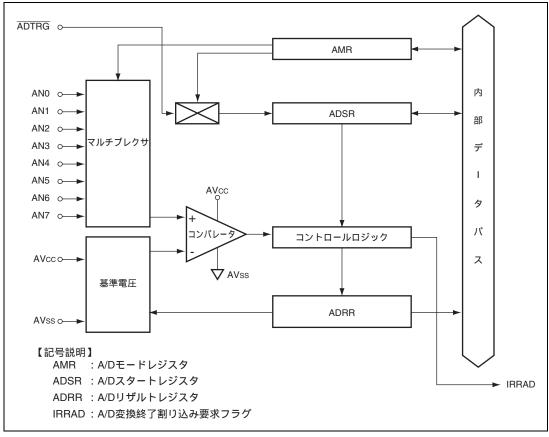

| 18. A/D | 変換器                            | 18-1  |

| 18.1    | 特長                             | 18-1  |

| 18.2    | 入出力端子                          | 18-3  |

| 18.3    | レジスタの説明                        | 18-3  |

| 18.3.1  | A/D リザルトレジスタ(ADRR)             | 18-3  |

| 18.3.2  | A/D モードレジスタ ( AMR )            | 18-4  |

| 18.3.3  | A/D スタートレジスタ(ADSR)             | 18-5  |

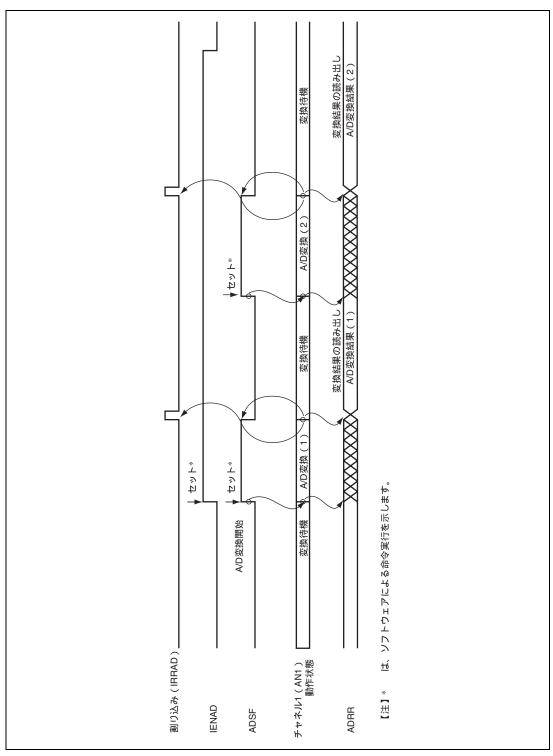

| 18.4    | 動作説明                           | 18-5  |

| 18.4.1  | A/D 变換動作                       | 18-5  |

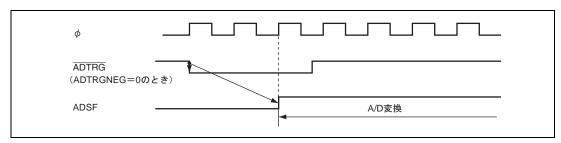

| 18.4.2  | 外部トリガタイミング                     | 18-5  |

| 18.4.3  | A/D 変換器の動作モード                  | 18-6  |

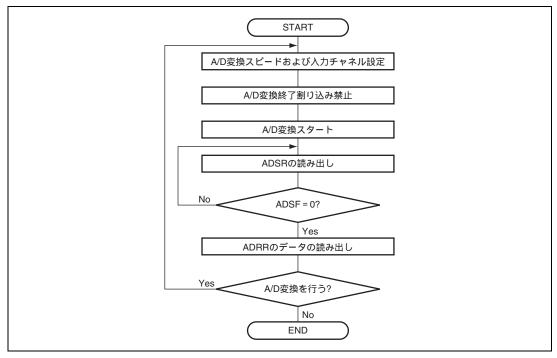

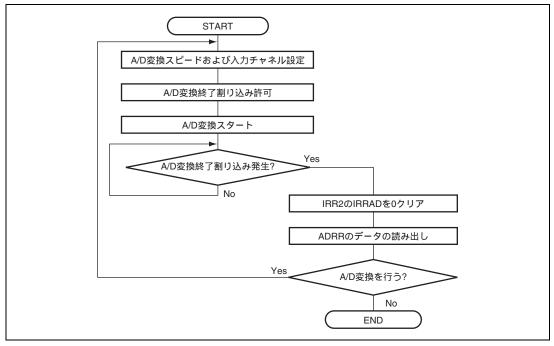

| 18.5    | 使用例                            | 18-6  |

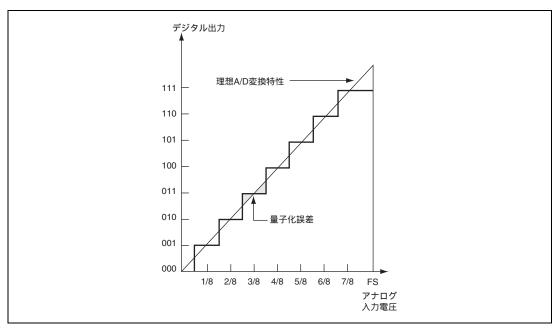

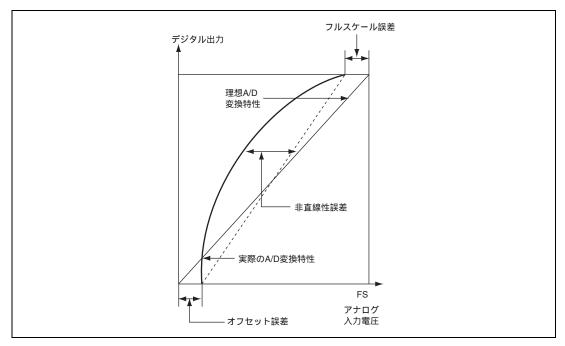

| 18.6    | A/D変換精度の定義                     | 18-9  |

| 18.7    | 使用上の注意事項                       | 18-11 |

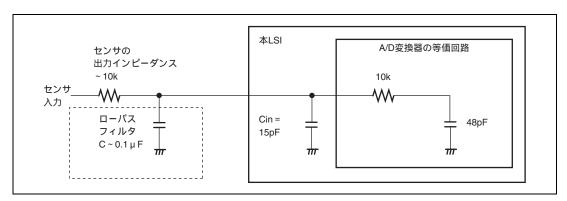

| 18.7.1  | 許容信号源インピーダンスについて               | 18-11 |

| 18.7.2  | 絶対精度への影響について                   | 18-11 |

| 18.7.3  | その他使用上の注意                      | 18-11 |

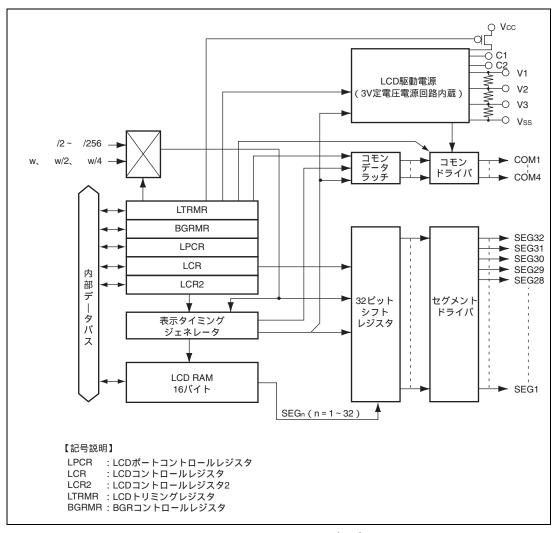

| 19. LC[ | ) コントローラ / ドライバ                | 19-1  |

| 19.1    | 特長                             | 19-1  |

| 19.2    | 入出力端子                          | 19-3  |

| 19.3    | レジスタの説明                        | 19-3  |

| 19.3.1  | LCD ポートコントロールレジスタ(LPCR)        | 19-4  |

| 19.3.2  | LCD コントロールレジスタ ( LCR )         | 19-5  |

| 19.3.3  | LCD コントロールレジスタ 2 (LCR2)        | 19-7  |

| 19.3.4  | LCD トリミングレジスタ ( LTRMR )        | 19-8  |

| 19.3.5  | BGR コントロールレジスタ ( BGRMR )       | 19-9  |

| 19.4    | 動作説明                           | 19-10 |

| 19.4.1  | LCD 表示までのセッティング                | 19-10 |

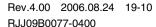

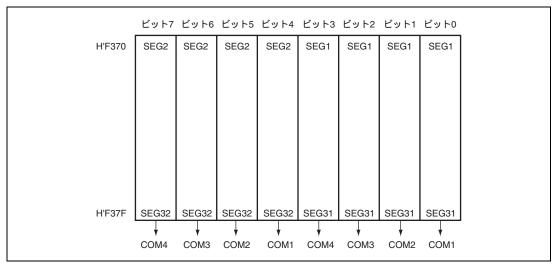

| 19.4.2  | LCD RAM と表示の関係                 | 19-12 |

| 19.4.3  | 3V 定電圧電源回路                     | 19-16 |

| 19.4.4  | 低消費電力モード時の動作                   | 19-17 |

| 19.4.5  | LCD 駆動電源の強化と微調整                | 19-18 |

| 19.5    | 使用上の注意事項                       | 19-18 |

| 19.5.1  | LCD コントローラ / ドライバ未使用時の端子処理について | 19-18 |

| 19.5.2               | 3V 定電圧回路未使用時の端子処理について                         | 19-18 |

|----------------------|-----------------------------------------------|-------|

| 20. I <sup>2</sup> C | バスインタフェース 2 ( IIC2 )                          | 20-1  |

| 20.1                 | 特長                                            | 20-1  |

| 20.2                 | 入出力端子                                         | 20-3  |

| 20.3                 | レジスタの説明                                       | 20-3  |

| 20.3.1               | I <sup>2</sup> C バスコントロールレジスタ 1 ( ICCR1 )     | 20-4  |

| 20.3.2               | I <sup>2</sup> C バスコントロールレジスタ 2 ( ICCR2 )     | 20-5  |

| 20.3.3               | I <sup>2</sup> C バスモードレジスタ(ICMR)              | 20-7  |

| 20.3.4               | I <sup>2</sup> C バス割り込み許可レジスタ(ICIER)          | 20-8  |

| 20.3.5               | I <sup>2</sup> C バスステータスレジスタ(ICSR)            | 20-10 |

| 20.3.6               | スレープアドレスレジスタ(SAR)                             | 20-12 |

| 20.3.7               | I <sup>2</sup> C バス送信データレジスタ(ICDRT)           | 20-12 |

| 20.3.8               | I <sup>2</sup> C バス受信データレジスタ(ICDRR)           | 20-12 |

| 20.3.9               | I <sup>2</sup> C バスシフトレジスタ(ICDRS)             | 20-12 |

| 20.4                 | 動作説明                                          | 20-13 |

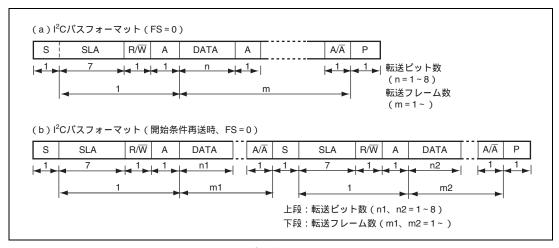

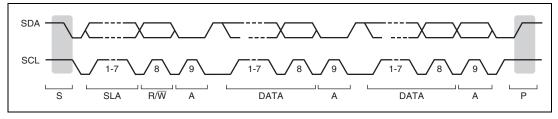

| 20.4.1               | I <sup>2</sup> C バスフォーマット                     | 20-13 |

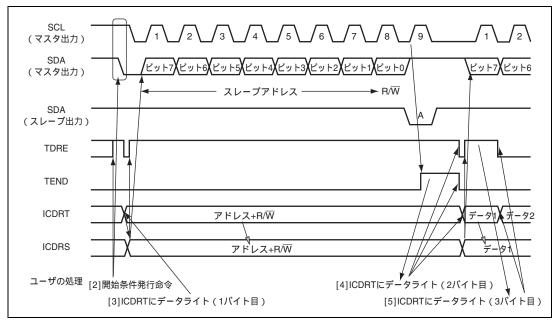

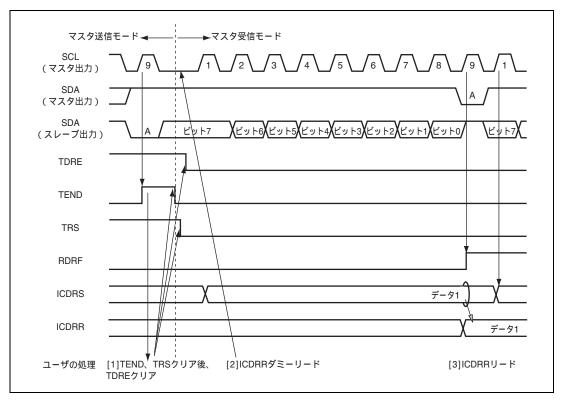

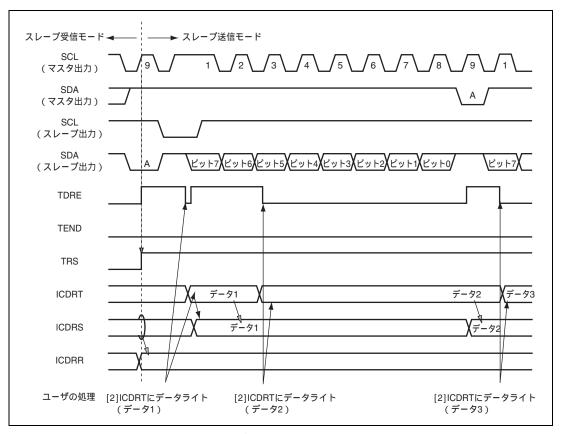

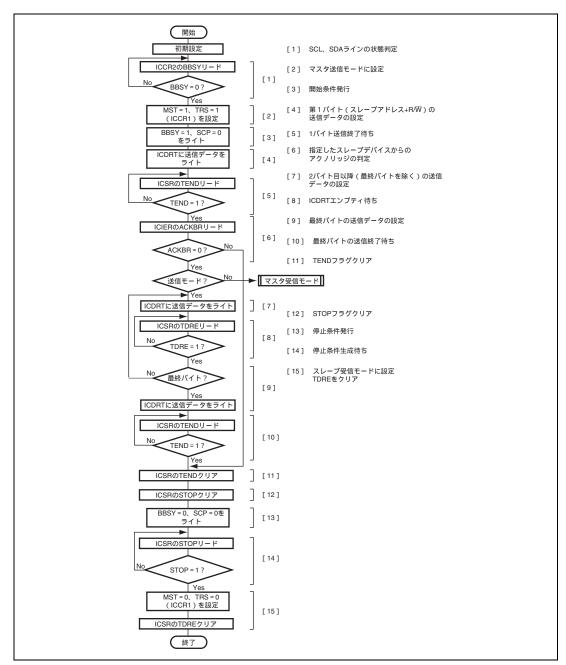

| 20.4.2               | マスタ送信動作                                       | 20-14 |

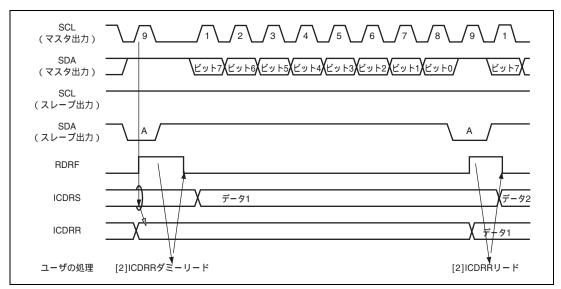

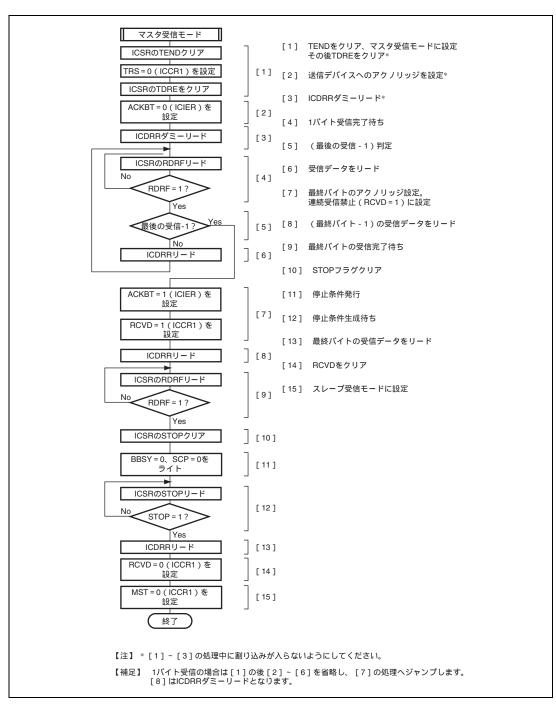

| 20.4.3               | マスタ受信動作                                       | 20-16 |

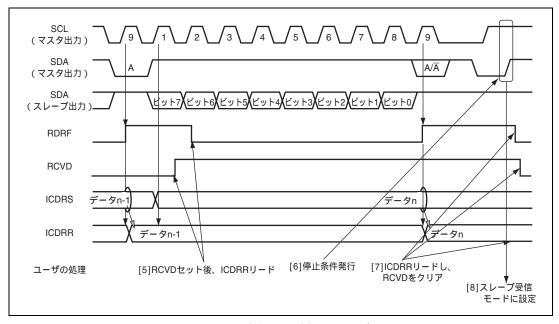

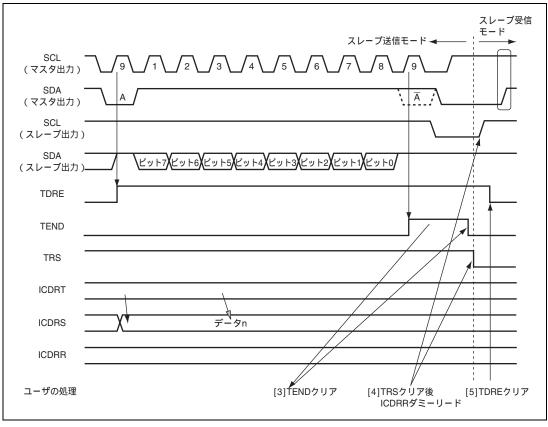

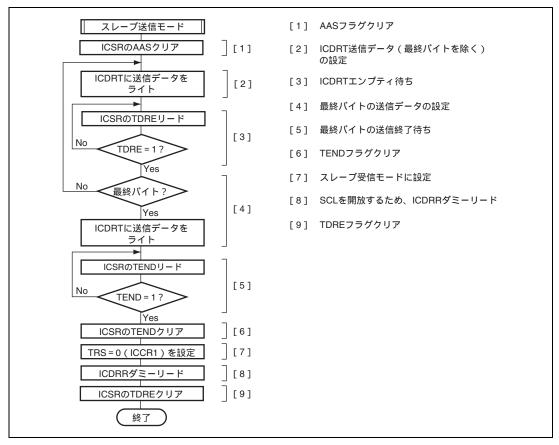

| 20.4.4               | スレーブ送信動作                                      | 20-18 |

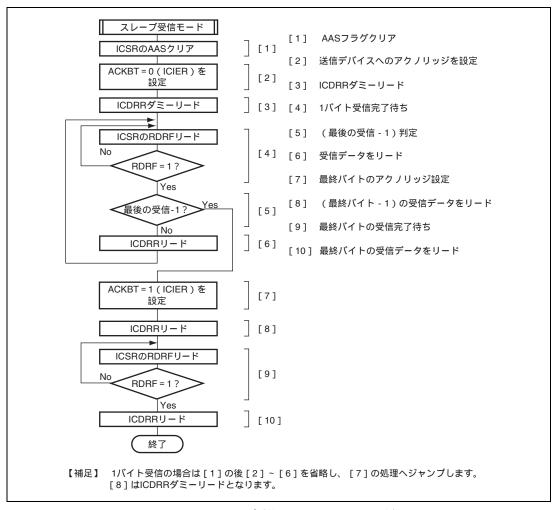

| 20.4.5               | スレーブ受信動作                                      | 20-20 |

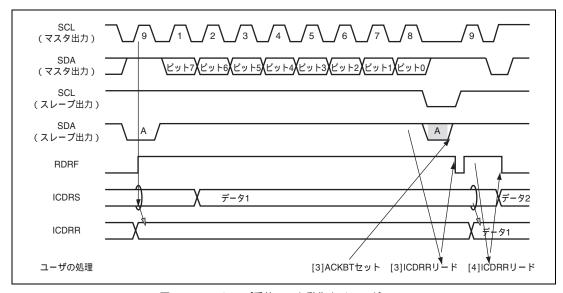

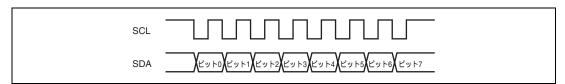

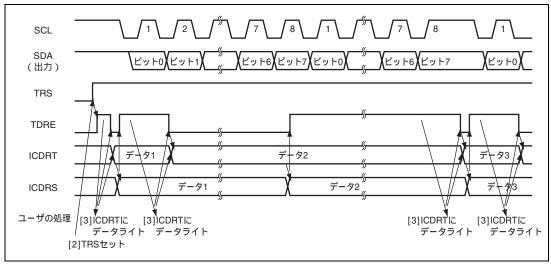

| 20.4.6               | クロック同期式シリアルフォーマット                             | 20-22 |

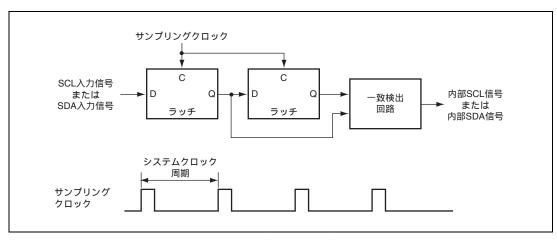

| 20.4.7               | ノイズ除去回路                                       | 20-24 |

| 20.4.8               | 使用例                                           | 20-25 |

| 20.5                 | 割り込み要求                                        | 20-29 |

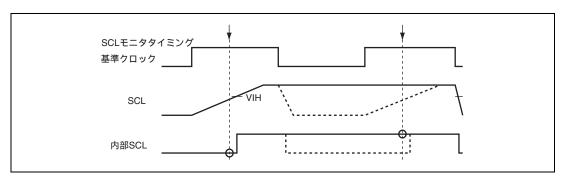

| 20.6                 | ビット同期回路                                       | 20-30 |

| 20.7                 | 使用上の注意事項                                      | 20-31 |

| 20.7.1               | 停止条件および開始条件(再送)の出力について                        | 20-31 |

| 20.7.2               | I <sup>2</sup> C バスモードレジスタ(ICMR)の WAIT 設定について | 20-31 |

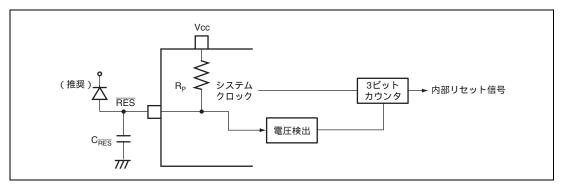

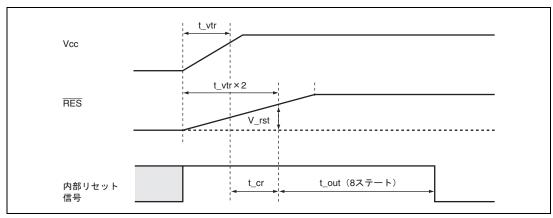

| 21. パワ               | リーオンリセット回路                                    | 21-1  |

| 21.1                 | 特長                                            | 21-1  |

| 21.2                 | 動作説明                                          |       |

| 21.2.1               | パワーオンリセット回路                                   |       |

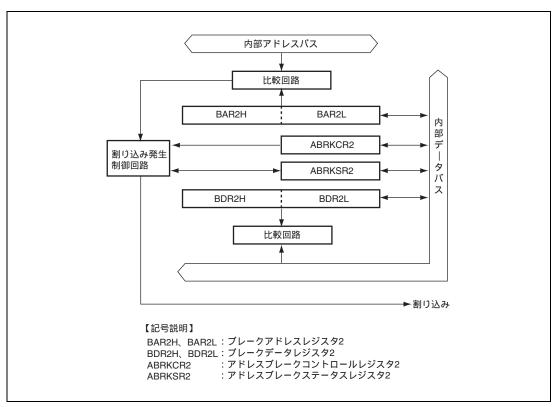

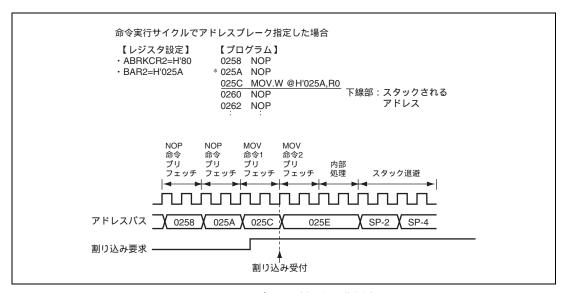

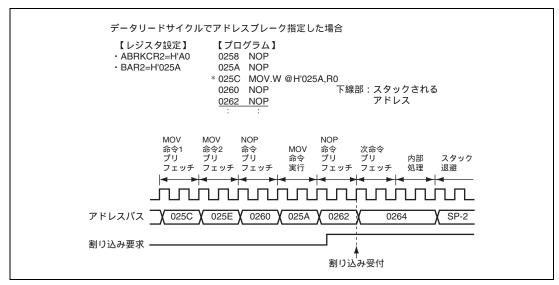

| 22. アト               | ・レスプレーク                                       | 22-1  |

| 22.1                 | レジスタの説明                                       |       |

| 22.1.1               | アドレスプレークコントロールレジスタ 2(ABRKCR2)                 |       |

| 22.1.2               | アドレスブレークステータスレジスタ 2 ( ABRKSR2 )               |       |

| 22.1.3               | プレークアドレスレジスタ 2 ( BAR2H、BAR2L )                |       |

|                      |                                               |       |

| 22.1.4 | ブレークデータレジスタ 2 ( BDR2H、BDR2L ) | 22-4  |

|--------|-------------------------------|-------|

| 22.2   | 動作説明                          | 22-4  |

| 22.3   | アドレスプレークの動作モード                | 22-5  |

| 23 LS  | <b>ジスター覧</b>                  | 23-1  |

|        |                               |       |

| 23.1   | レジスタアドレス一覧(アドレス順)             |       |

| 23.2   | レジスタビット一覧                     |       |

| 23.3   | 各動作モードにおけるレジスタの状態             | 23-12 |

| 24. 電気 | 〔的特性                          | 24-1  |

| 24.1   | F-ZTAT版の絶対最大定格                | 24-1  |

| 24.2   | F-ZTAT版の電気的特性                 | 24-2  |

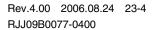

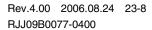

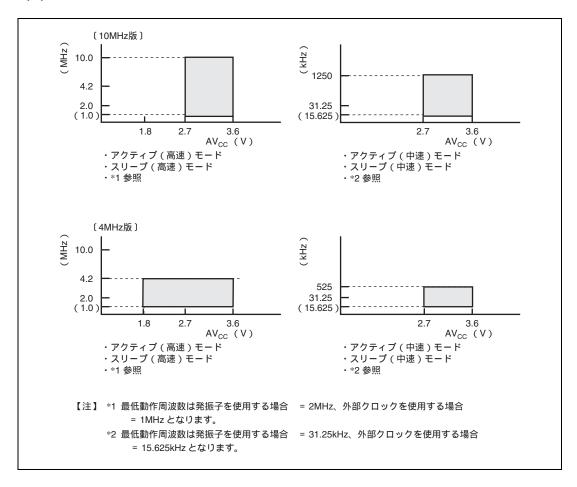

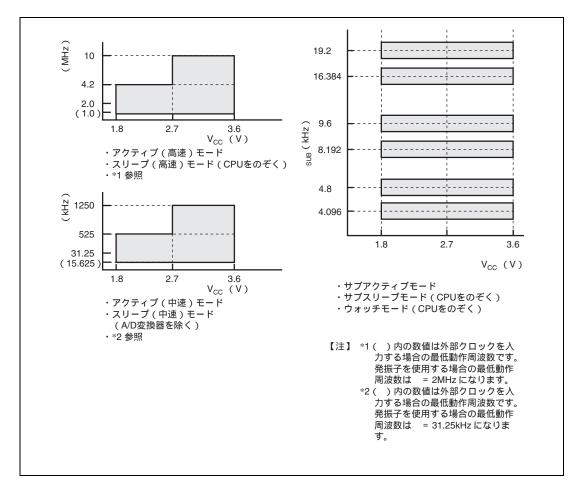

| 24.2.1 | 電源電圧と動作範囲                     | 24-2  |

| 24.2.2 | DC 特性                         | 24-5  |

| 24.2.3 | AC 特性                         | 24-10 |

| 24.2.4 | A/D 変換器特性                     | 24-13 |

| 24.2.5 | LCD 特性                        | 24-14 |

| 24.2.6 | パワーオンリセット回路特性                 | 24-14 |

| 24.2.7 | ウォッチドッグタイマ特性                  | 24-15 |

| 24.2.8 | フラッシュメモリ特性【暫定仕様】              | 24-15 |

| 24.3   | マスクROM版の絶対最大定格                | 24-17 |

| 24.4   | マスクROM版の電気的特性                 | 24-18 |

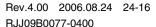

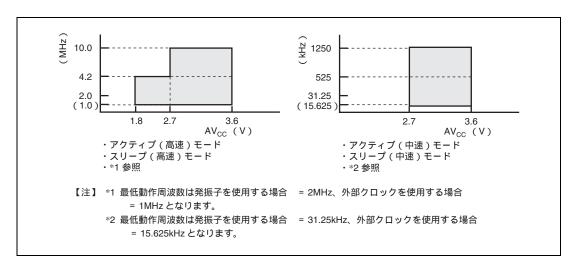

| 24.4.1 | 電源電圧と動作範囲                     | 24-18 |

| 24.4.2 | DC 特性                         | 24-21 |

| 24.4.3 | AC 特性                         | 24-26 |

| 24.4.4 | A/D 变換器特性                     | 24-29 |

| 24.4.5 | LCD 特性                        | 24-30 |

| 24.4.6 | パワーオンリセット回路特性                 | 24-31 |

| 24.4.7 | ウォッチドッグタイマ特性                  | 24-31 |

| 24.5   | 動作タイミング                       | 24-32 |

| 24.6   | 出力負荷回路                        | 24-34 |

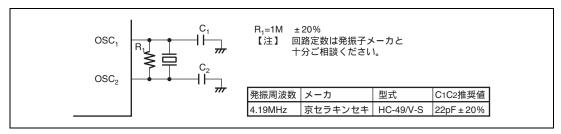

| 24.7   | 推奨発振子                         | 24-34 |

| 24.8   | 使用上の注意事項                      | 24-34 |

| 付録     |                               | 付録-1  |

| A.     | 命令                            | 付録-1  |

| A.1    | 命令一覧                          | 付録-1  |

| A.2    | オペレーションコードマップ                 | 付録-16 |

| A.3    | 命令実行ステート数                     | 付録-19 |

| A.4    | 命令とアドレッシングモードの組み合わせ           | 付録-28 |

| B.         | I/Oポート              | 付録-29 |  |

|------------|---------------------|-------|--|

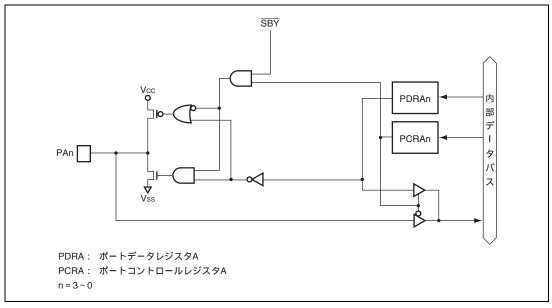

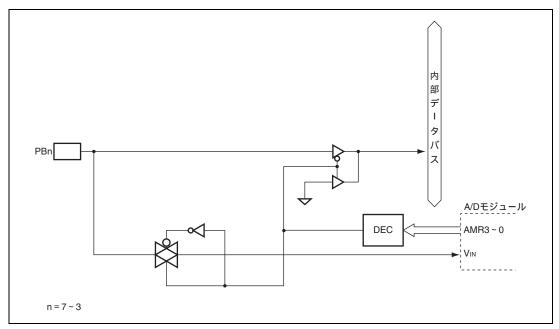

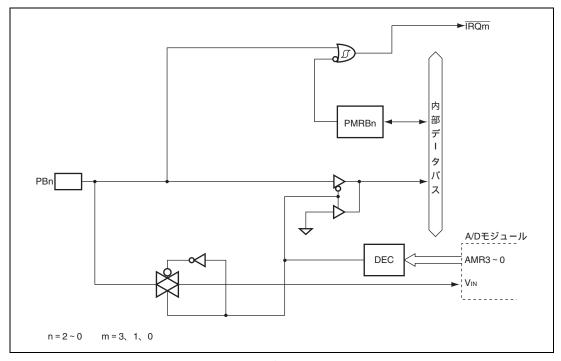

| В          | 3.1 I/O ポートブロック図    | 付録-29 |  |

| В          | 3.2 各処理状態におけるポートの状態 | 付録-45 |  |

| C.         | 製品型名一覧              | 付録-46 |  |

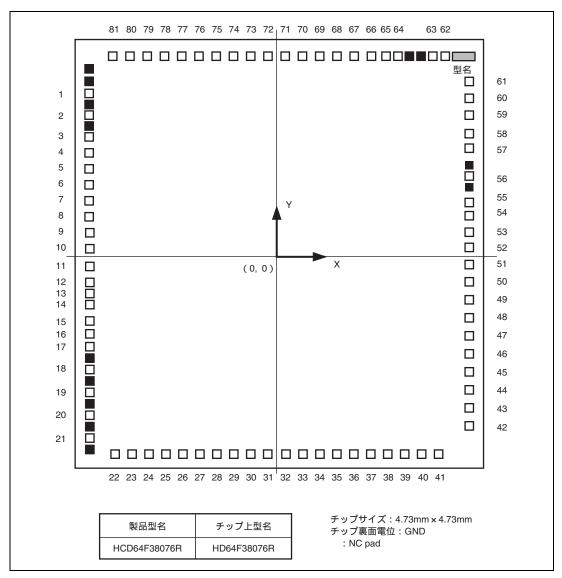

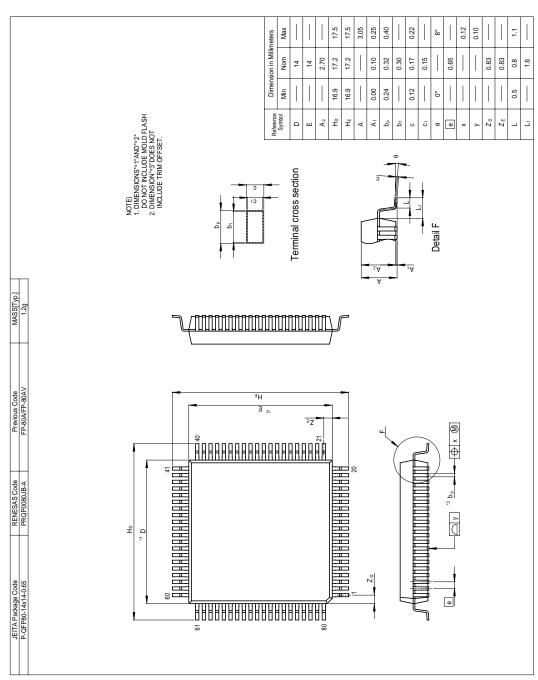

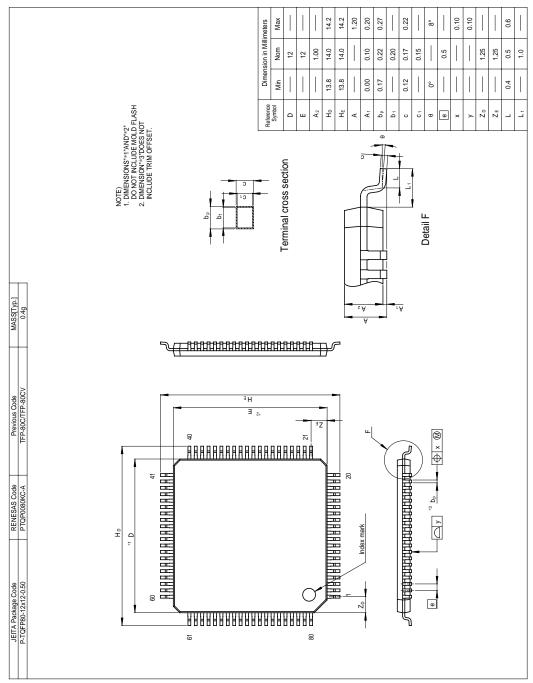

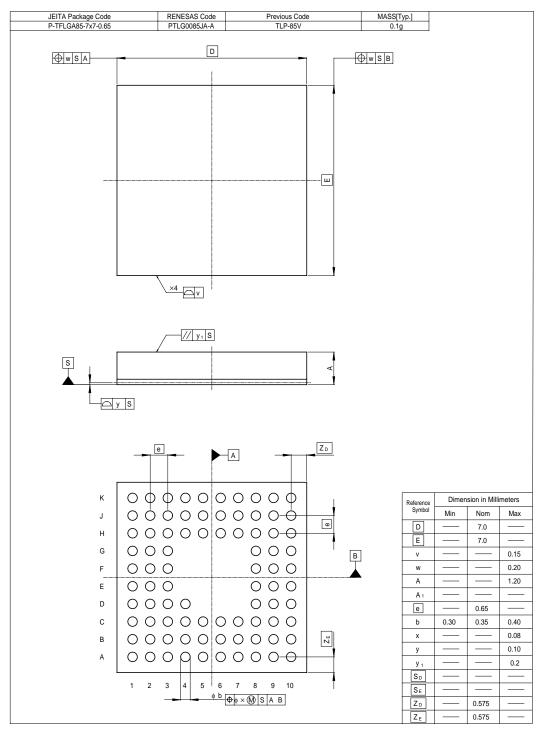

| D.         | 外形寸法図               | 付録-48 |  |

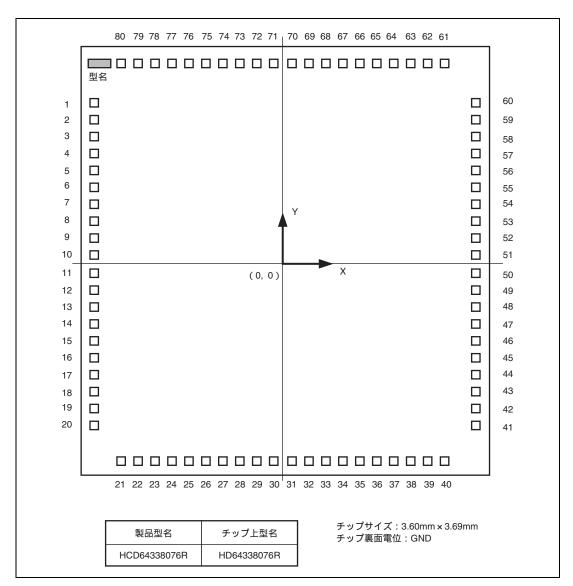

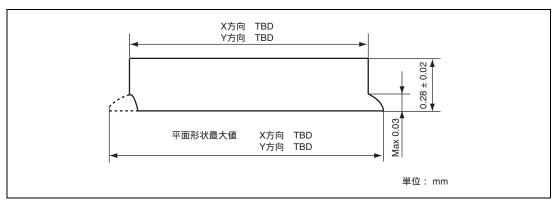

| E.         | チップ形状仕様図            | 付録-51 |  |

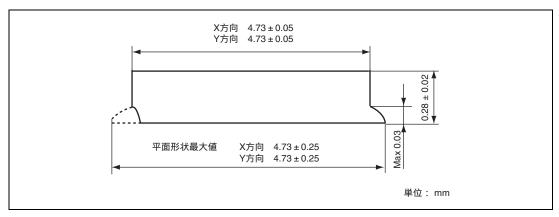

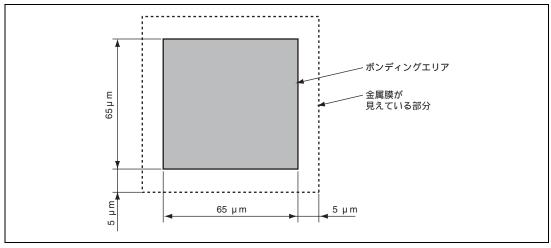

| F.         | ボンディングパッド形状図        | 付録-52 |  |

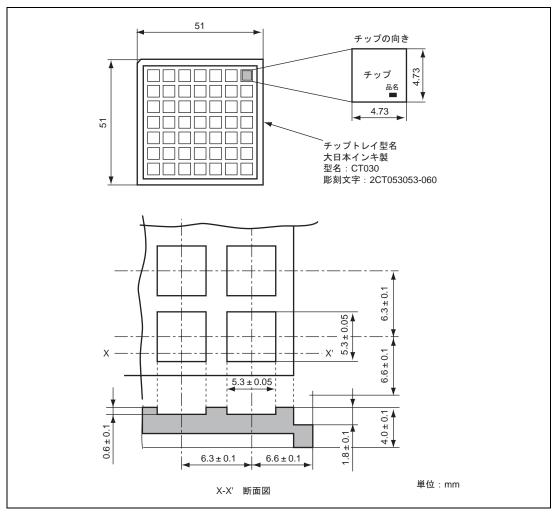

| G.         | チップトレイ仕様図           | 付録-53 |  |

| 本版で改訂された箇所 |                     |       |  |

| 索引         |                     | 索引-1  |  |

## 図目次

| 1. | 概要…    |                                         | 1-1  |

|----|--------|-----------------------------------------|------|

|    | 図 1.1  | H8/38076R グループ内部ブロック図                   | 1-3  |

|    | 図 1.2  | H8/38076R グループピン配置図 ( FP-80A、TFP-80C )  | 1-4  |

|    | 図 1.3  | H8/38076R グループピン配置図 (TLP-85V)           | 1-5  |

|    | 図 1.4  | HCD64F38076R パッド配置図(上面図)                | 1-9  |

|    | 図 1.5  | HCD64338076R パッド配置図 (上面図)               | 1-13 |

| 2. | CPU    |                                         | 2-1  |

|    | 図 2.1  | メモリマップ                                  | 2-2  |

|    | 図 2.2  | CPU 内部レジスタ構成                            | 2-3  |

|    | 図 2.3  | 汎用レジスタの使用方法                             | 2-4  |

|    | 図 2.4  | スタックポインタとスタック領域の関係                      | 2-4  |

|    | 図 2.5  | 汎用レジスタのデータ形式 (1)                        | 2-6  |

|    | 図 2.5  | 汎用レジスタのデータ形式 (2)                        | 2-7  |

|    | 図 2.6  | メモリ上でのデータ形式                             | 2-8  |

|    | 図 2.7  | 命令フォーマット                                | 2-17 |

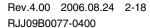

|    | 図 2.8  | メモリ間接による分岐アドレスの指定                       | 2-20 |

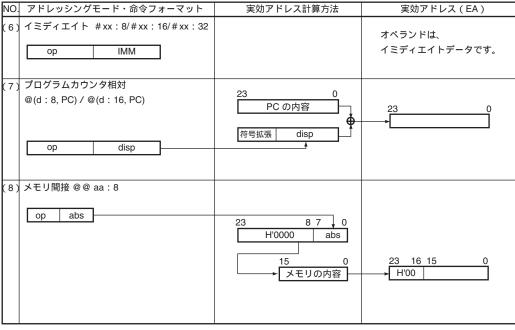

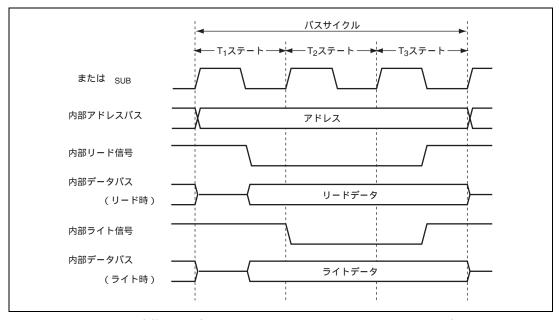

|    | 図 2.9  | 内蔵メモリアクセスサイクル                           | 2-23 |

|    | 図 2.10 | 内蔵周辺モジュールアクセスサイクル ( 3 ステートアクセスの場合 )     | 2-24 |

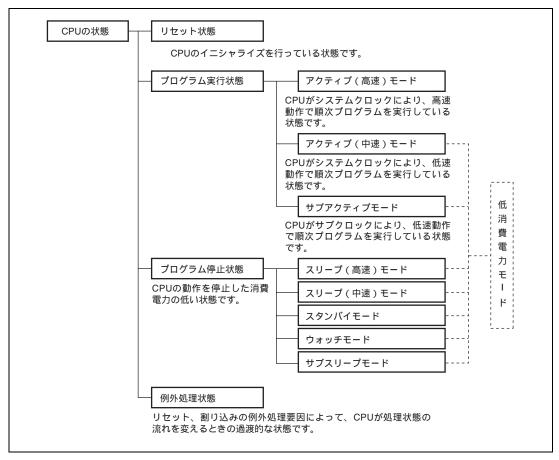

|    | 図 2.11 | CPU の状態の分類                              | 2-25 |

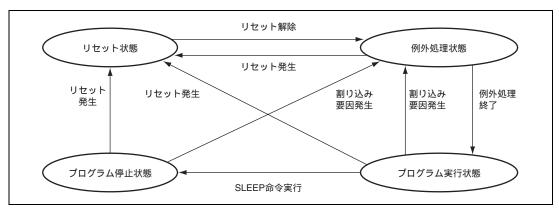

|    | 図 2.12 | 状態遷移図                                   | 2-26 |

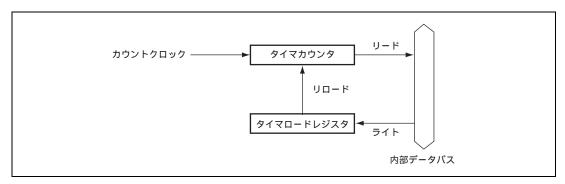

|    | 図 2.13 | 同一アドレスに割付けられた 2 つのレジスタを持つタイマの構成例        | 2-27 |

| 3. | 例外処    | 哩                                       | 3-1  |

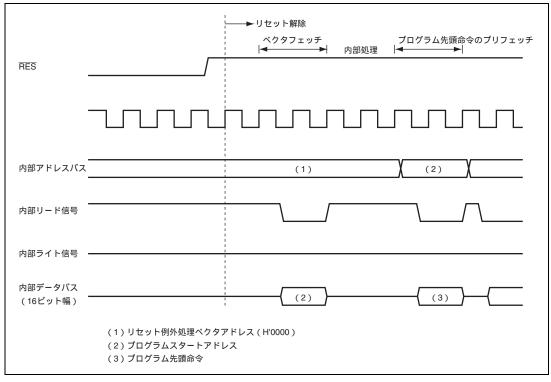

|    | 図 3.1  | リセット例外処理シーケンス                           | 3-4  |

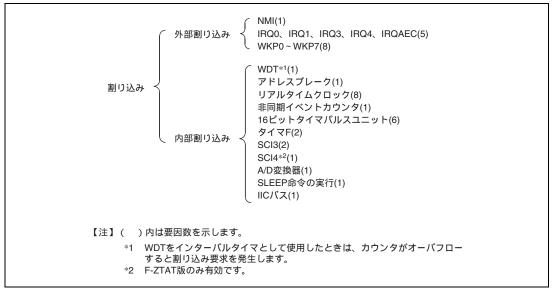

|    | 図 3.2  | 割り込み要因と要因数                              | 3-5  |

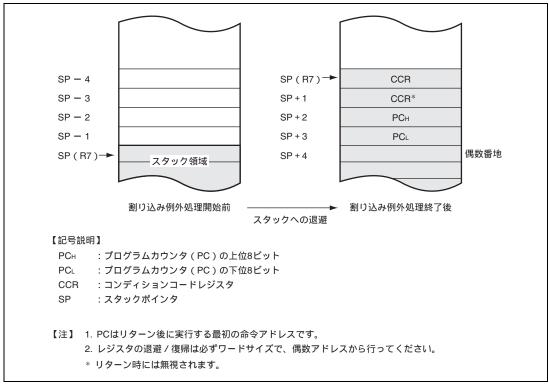

|    | 図 3.3  | 割り込み例外処理終了後のスタック状態                      | 3-6  |

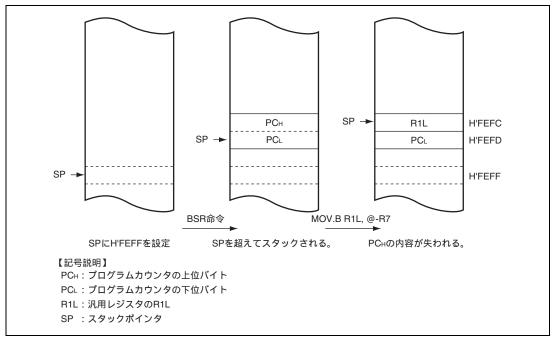

|    | 図 3.4  | SP に奇数を設定したときの動作                        | 3-7  |

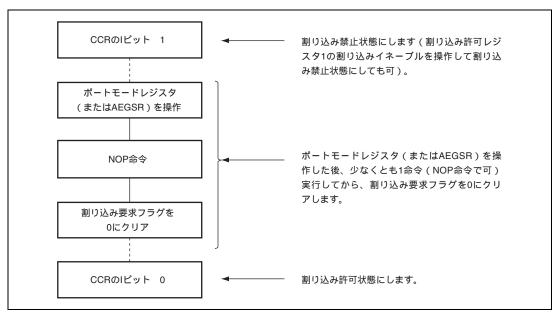

|    | 図 3.5  | ポートモードレジスタ(または AEGSR)操作と割り込み要求フラグのクリア手順 | 3-9  |

| 4. | 割り込    | みコントローラ                                 | 4-1  |

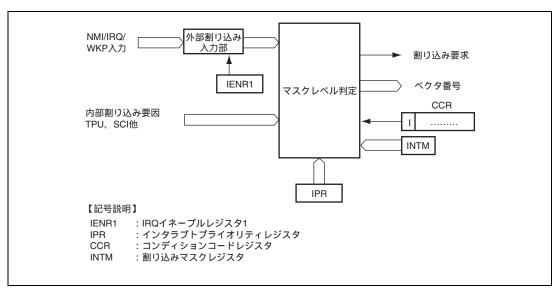

|    | 図 4.1  | 割り込みコントローラのブロック図                        | 4-1  |

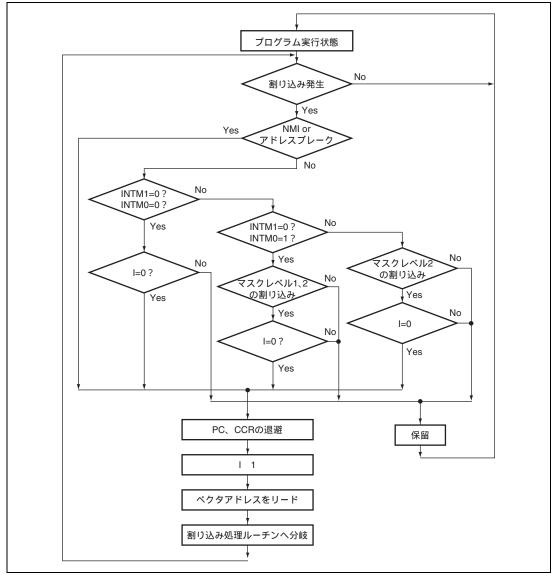

|    | 図 4.2  | 割り込み受け付けまでのフロー                          | 4-16 |

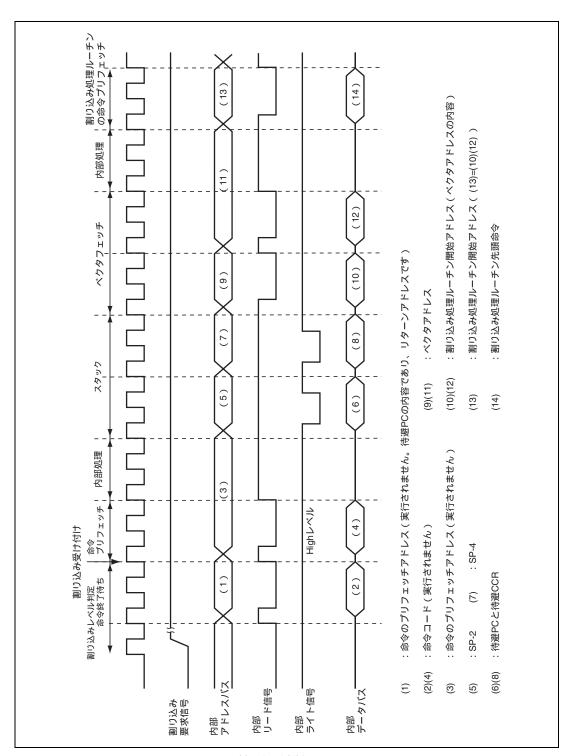

|    | 図 4.3  | 割り込み例外処理シーケンス                           | 4-17 |

|    | 図 4.4          | 割り込みの発生とディスエーブルの競合                    | 4-19                 |

|----|----------------|---------------------------------------|----------------------|

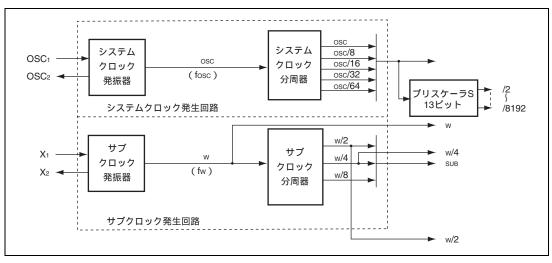

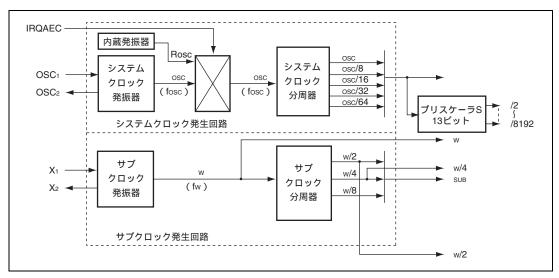

| 5. | クロック           | 7発振器                                  | 5-1                  |

|    | 図 5.1 (1)      | ) クロック発生回路のプロック図(フラッシュメモリ版)           | 5-1                  |

|    | 図 5.1 (2)      | ) クロック発生回路のブロック図(マスク ROM 版)           | 5-2                  |

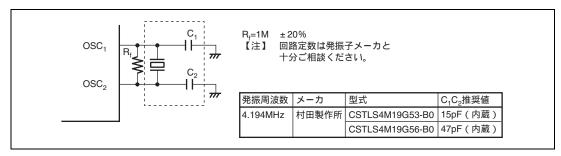

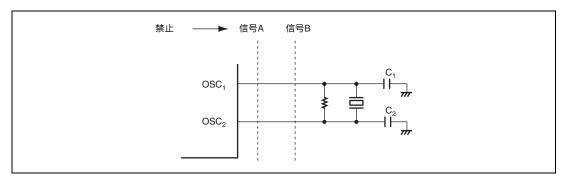

|    | 図 5.2          | 水晶発振子の接続例                             | 5-4                  |

|    | 図 5.3          | セラミック発振子の接続例                          | 5-4                  |

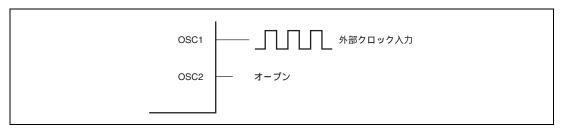

|    | 図 5.4          | 外部クロックを入力する場合の接続例                     | 5-5                  |

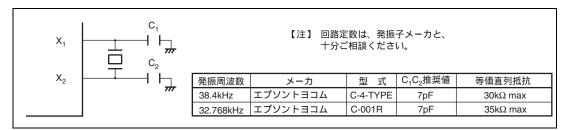

|    | 図 5.5          | 32.768kHz/38.4kHz 水晶発振子の接続例           | 5-6                  |

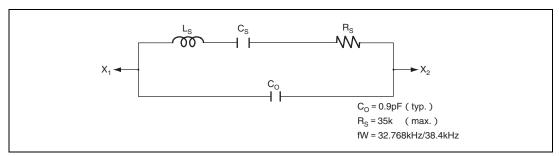

|    | 図 5.6          | 32.768kHz/38.4kHz 水晶発振子の等価回路          | 5-6                  |

|    | 図 5.7          | サプクロックを必要としない場合の端子処理                  | 5-7                  |

|    | 図 5.8          | 外部クロックを入力する場合の接続例                     | 5-7                  |

|    | 図 5.9          | 水晶、セラミック発振子の配置例                       | 5-8                  |

|    | 図 5.10         | 負性抵抗測定と回路変更案                          | 5-9                  |

|    | 図 5.11         | 発振回路のボード設計に関する注意事項                    | 5-10                 |

|    | 図 5.12         | 発振安定待機時間                              | 5-11                 |

| 6. | 低消費電           | 電力モード                                 | 6-1                  |

|    | 図 6.1          | モード遷移図                                | 6-6                  |

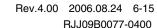

|    | 図 6.2          | スタンバイモードへの遷移と端子状態                     | 6-16                 |

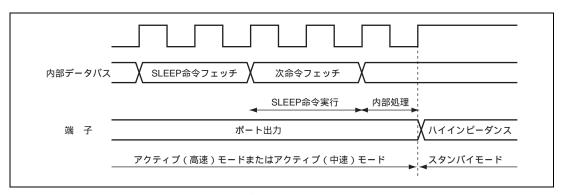

|    | 図 6.3          | スタンバイモード、ウォッチモード前後で外部入力信号が変化する場合の注意事項 | 6-17                 |

| 7. | ROM            |                                       | 7-1                  |

|    | 図 7.1          | フラッシュメモリのプロック構成                       | 7-2                  |

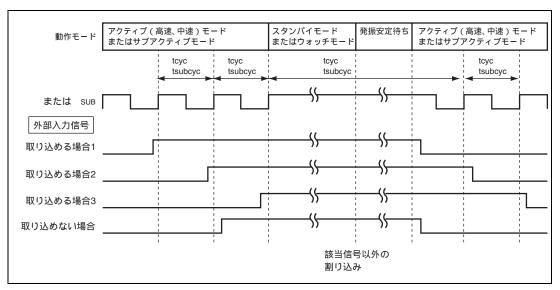

|    | 図 7.2          | ユーザモードにおける書き込み / 消去例                  | 7-9                  |

|    | 図 7.3          | プログラム / プログラムベリファイフロー                 | 7-11                 |

|    | 図 7.4          | イレース / イレースベリファイフロー                   | 7-14                 |

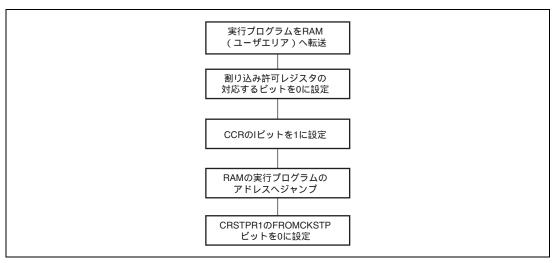

|    | 図 7.5          | モジュールスタンバイモードの設定方法                    | 7-17                 |

| 9. | I/O ポー         | F                                     | 9-1                  |

|    | 図 9.1          | ポート 1 の端子構成                           | 9-1                  |

|    | 図 9.2          | ポート 3 の端子構成                           | 9-7                  |

|    | 図 9.3          | ポート 4 の端子構成                           | 9-11                 |

|    | 図 9.4          | ポート 5 の端子構成                           | 9-14                 |

|    | _              | 19 L c = 10 = 1## -1*                 | 0.17                 |

|    | 図 9.5          | ポート 6 の端子構成                           | 9-1/                 |

|    | 図 9.5<br>図 9.6 | ボート 7 の端子構成ポート 7 の端子構成                |                      |

|    |                |                                       | 9-20                 |

|    | 図 9.6          | ポート 7 の端子構成                           | 9-20<br>9-22         |

|    | 図 9.6<br>図 9.7 | ポート 7 の端子構成                           | 9-20<br>9-22<br>9-24 |

| 図 9.11   | 入出力データ反転機能                           | 9-34       |

|----------|--------------------------------------|------------|

| 10. リアル  | タイムクロック(RTC)                         | 10-1       |

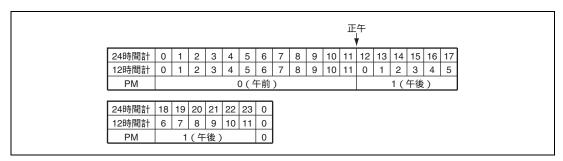

| 図 10.1   | RTC のブロック図                           | 10-1       |

| 図 10.2   | 時間表現の定義                              | 10-5       |

| 図 10.3   | 初期設定手順                               | 10-9       |

| 図 10.4   | 正しい時刻を得られない場合の例                      | 10-10      |

| 11. タイマ  | F                                    | 11-1       |

| 図 11.1   | タイマ F のブロック図                         | 11-2       |

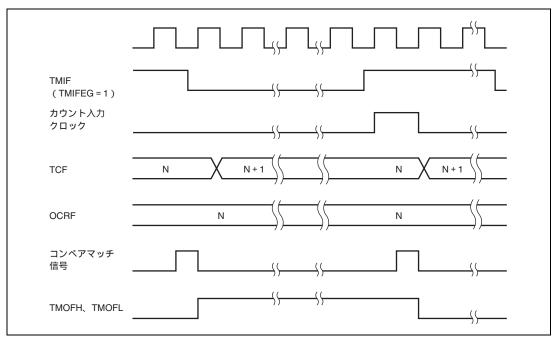

| 図 11.2   | TMOFH、TMOFL 出力タイミング                  | 11-9       |

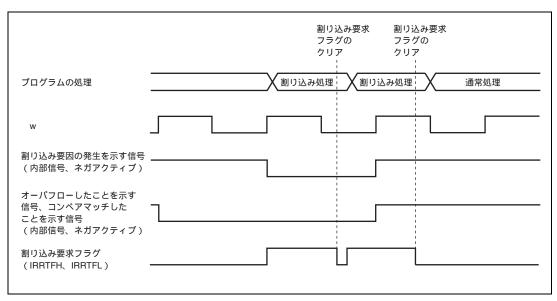

| 図 11.3   | 割り込み要因の発生を示す信号が有効なときに割り込み要求フラグのクリアを  | 行った場合11-12 |

| 12. 16ビッ | ノトタイマパルスユニット(TPU)                    | 12-1       |

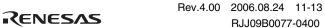

| 図 12.1   | TPU ブロック図                            | 12-3       |

| 図 12.2   | 16 ビットレジスタのアクセス動作(CPU TCNT(16 ビット))  | 12-14      |

| 図 12.3   | 8 ビットレジスタのアクセス動作(CPU TCR(上位 8 ビット))  | 12-15      |

| 図 12.4   | 8 ビットレジスタのアクセス動作(CPU TMDR(下位 8 ビット)) | 12-15      |

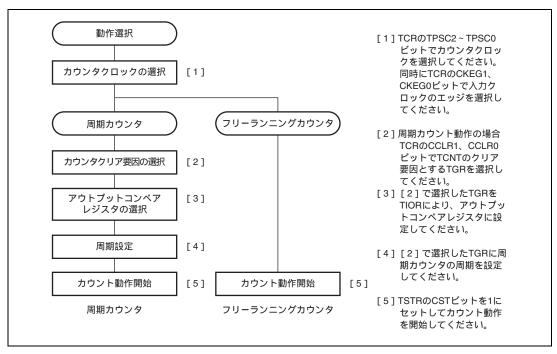

| 図 12.5   | カウンタ動作設定手順例                          | 12-16      |

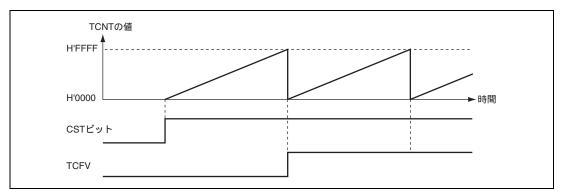

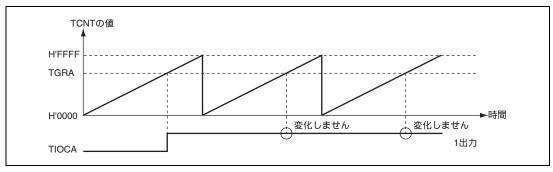

| 図 12.6   | フリーランニングカウンタの動作                      | 12-17      |

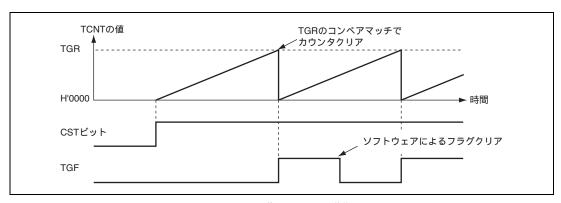

| 図 12.7   | 周期カウンタの動作                            | 12-17      |

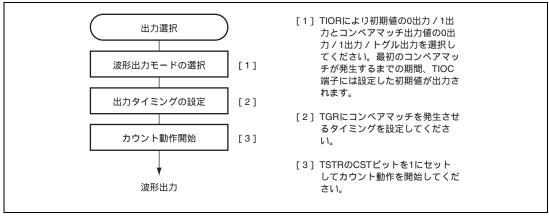

| 図 12.8   | コンペアマッチによる波形出力動作例                    | 12-18      |

| 図 12.9   | 1 出力の動作例                             | 12-18      |

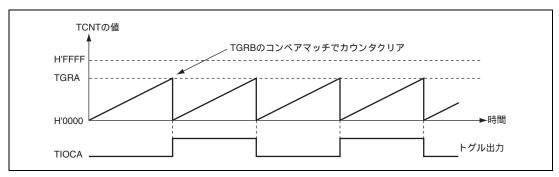

| 図 12.10  | トグル出力の動作例                            | 12-19      |

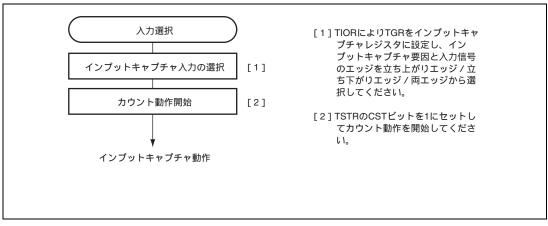

| 図 12.11  | インプットキャプチャ動作の設定例                     | 12-19      |

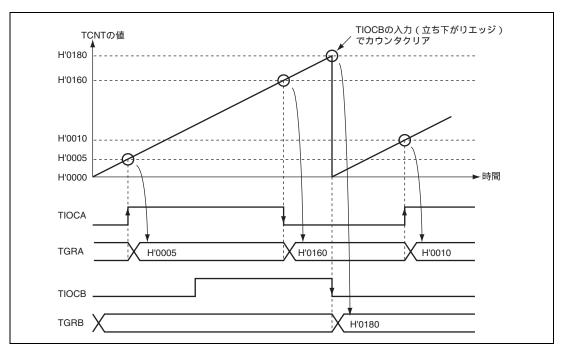

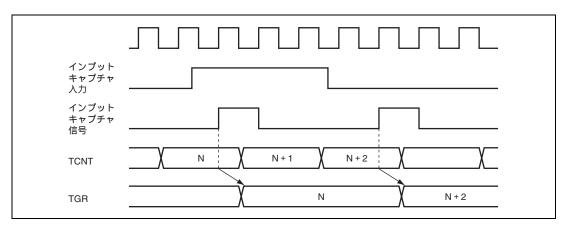

| 図 12.12  | インプットキャプチャ動作例                        | 12-20      |

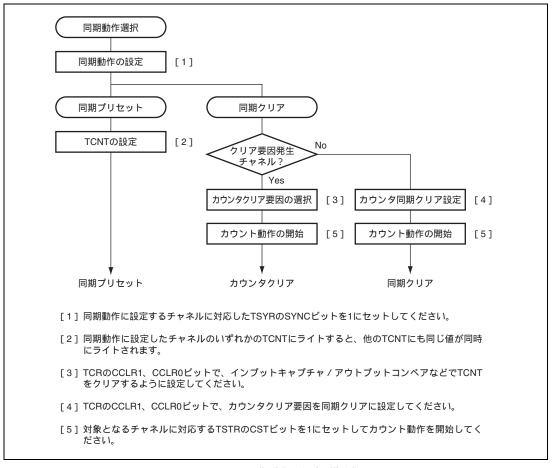

| 図 12.13  | 同期動作の設定手順例                           | 12-21      |

| 図 12.14  | 同期動作の動作例                             | 12-22      |

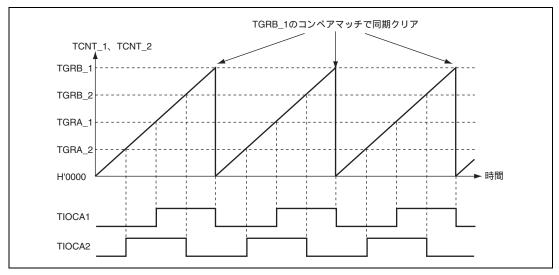

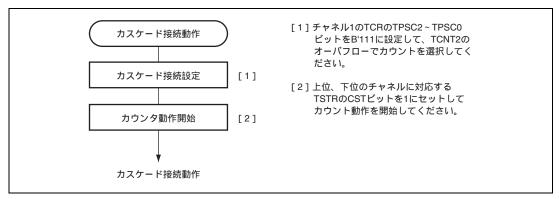

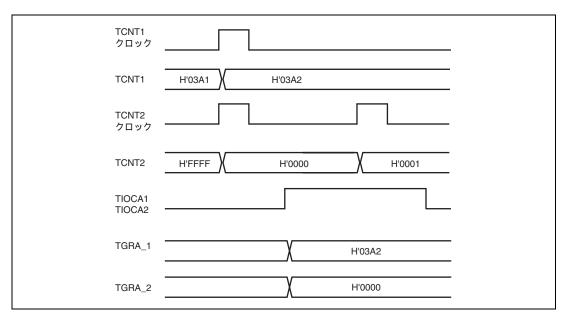

| 図 12.15  | カスケード接続動作設定手順                        | 12-23      |

| 図 12.16  | カスケード接続動作例                           | 12-23      |

| 図 12.17  | PWM モードの設定手順例                        | 12-25      |

| 図 12.18  | PWM モードの動作例(1)                       | 12-25      |

| 図 12.19  | PWM モードの動作例 ( 2 )                    | 12-26      |

| 図 12.20  | PWM モードの動作例 (3)                      | 12-27      |

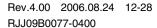

| 図 12.21  | 内部クロック動作時のカウントタイミング                  | 12-29      |

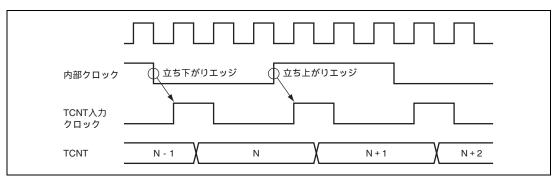

| 図 12.22  | 外部クロック動作時のカウントタイミング                  | 12-29      |

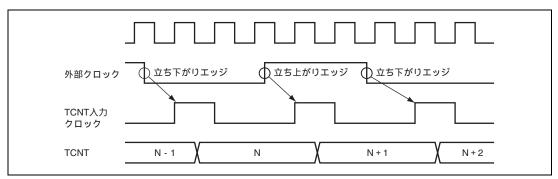

| 図 12.23  | アウトプットコンペア出力タイミング                    |            |

| 図 12.24  | インプットキャプチャ入力信号タイミング                  | 12-30      |

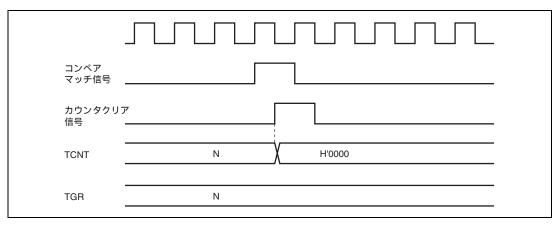

| 図 12.25  | カウンタクリアタイミング(コンペアマッチ)                |            |

| 図 12.26  | カウンタクリアタイミング(インプットキャプチャ)             | 12-31      |

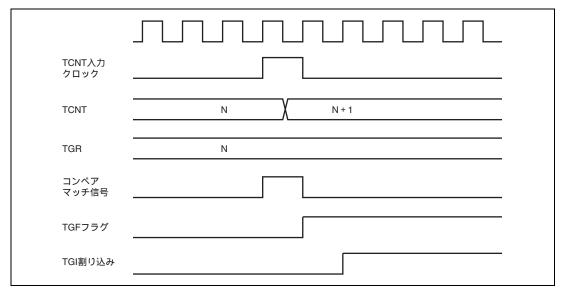

| 図 12.27  | TGI 割り込みタイミング(コンペアマッチ)                            | 12-32 |

|----------|---------------------------------------------------|-------|

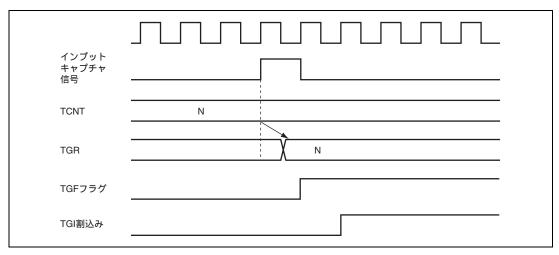

| 図 12.28  | TGI 割り込みタイミング(インプットキャプチャ)                         | 12-32 |

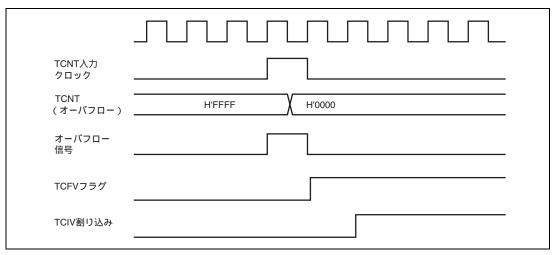

| 図 12.29  | TCIV 割り込みのセットタイミング                                | 12-33 |

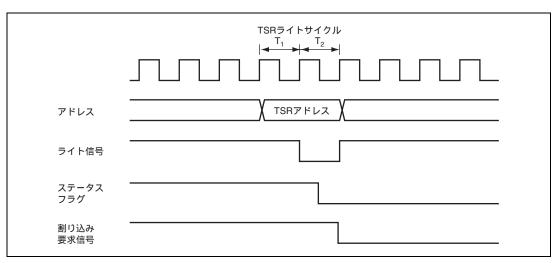

| 図 12.30  | CPU によるステータスフラグのクリアタイミング                          | 12-33 |

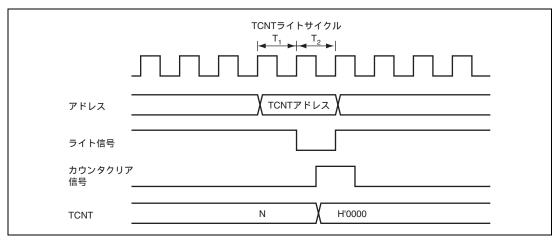

| 図 12.31  | TCNT のライトとクリアの競合                                  | 12-35 |

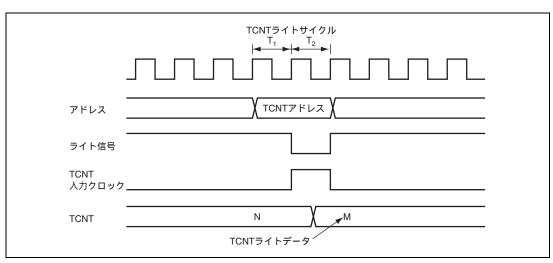

| 図 12.32  | TCNT のライトとカウントアップの競合                              | 12-35 |

| 図 12.33  | TGR のライトとコンペアマッチの競合                               | 12-36 |

| 図 12.34  | TGR のリードとインプットキャプチャの競合                            | 12-37 |

| 図 12.35  | TGR のライトとインプットキャプチャの競合                            | 12-37 |

| 図 12.36  | オーバフローとカウンタクリアの競合                                 | 12-38 |

| 図 12.37  | TCNT のライトとオーバフローの競合                               | 12-38 |

| 13. 非同其  | 月イベントカウンタ(AEC)                                    | 13-1  |

| 図 13.1   | 非同期イベントカウンタブロック図                                  | 13-2  |

| 図 13.2   | 16 ビットカウンタとして使用する場合のソフトウェア手順                      | 13-8  |

| 図 13.3   | 8 ビットカウンタとして使用する場合のソフトウェア手順                       | 13-9  |

| 図 13.4   | イベントカウンタ動作波形                                      | 13-10 |

| 図 13.5   | クロック制御動作例                                         | 13-11 |

| 14. ウォッ  | リチドッグタイマ                                          | 14-1  |

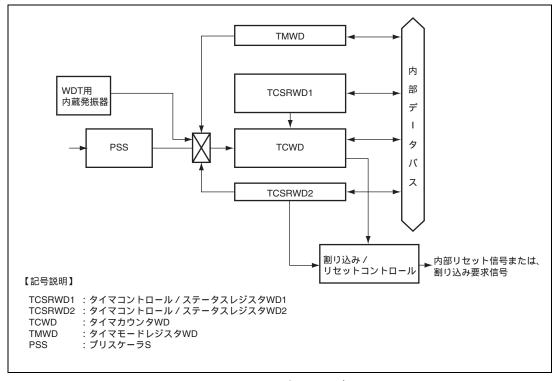

| 図 14.1   | ウォッチドッグタイマのブロック図                                  | 14-2  |

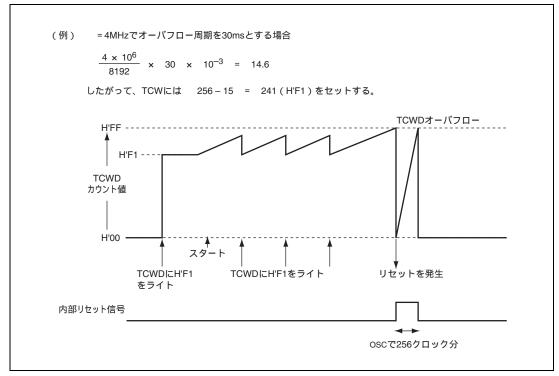

| 図 14.2   | ウォッチドッグタイマの動作例                                    | 14-6  |

| 図 14.3   | ウォッチドッグタイマモード時の動作                                 | 14-7  |

| 図 14.4   | OVF フラグのセットタイミング                                  | 14-7  |

| 15. シリフ  | プルコミュニケーションインタフェース3(SCI3、IrDA)                    | 15-1  |

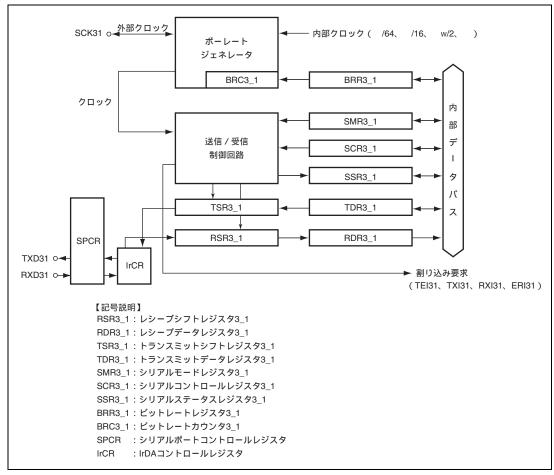

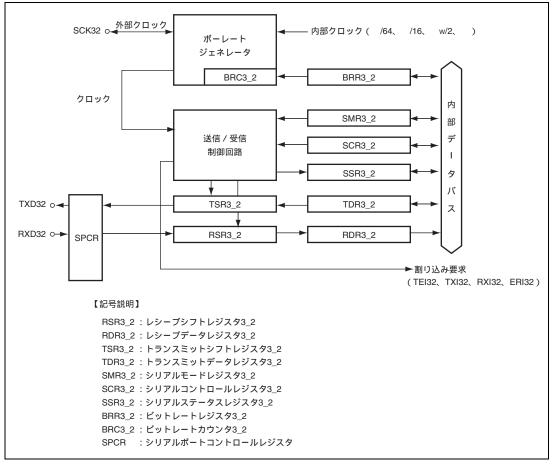

| 図 15.1 ( | 〔1) SCI3_1 のプロック図                                 | 15-3  |

| 図 15.1 ( | (2) SCI3_2のプロック図                                  | 15-4  |

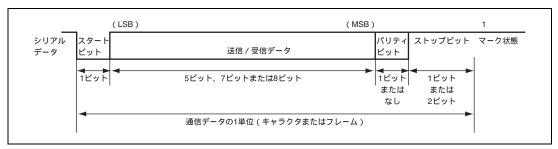

| 図 15.2   | 調歩同期式通信のデータフォーマット                                 | 15-21 |

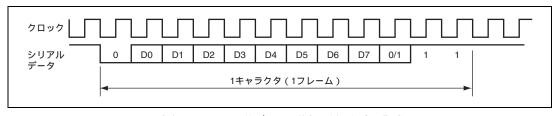

| 図 15.3   | 出力クロックと通信データの位相関係(調歩同期式モード)                       |       |

|          | (8 ビットデータ / パリティあり / 2 ストップビットの例)                 | 15-21 |

| 図 15.4   | SCI3 を初期化するときのフローチャートの例                           | 15-24 |

| 図 15.5   | 調歩同期式モードの送信時の動作例<br>(8 ビットデータ/パリティあり/1 ストップビットの例) | 15-25 |

| 図 15.6   | データ送信のフローチャートの例(調歩同期式モード)                         |       |

| 図 15.7   | 調歩同期式モードの受信時の動作例                                  |       |

|          | (8ビットデータ / パリティあり / 1 ストップビットの例)                  | 15-27 |

| 図 15.8   | データ受信のフローチャートの例(調歩同期式モード)                         | 15-29 |

| 図 15.9   | クロック同期式通信のデータフォーマット                               | 15-30 |

| 図 15.10  | クロック同期式モードの送信時の動作例                                | 15-31 |

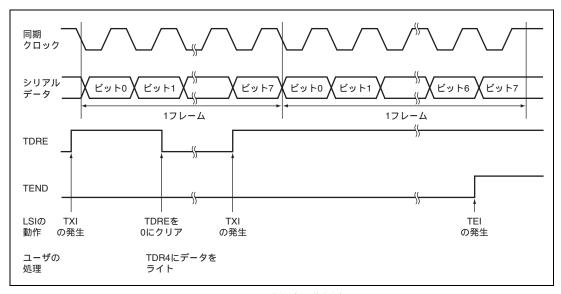

| 図 15.11  | データ送信のフローチャートの例(クロック同期式モード)                       | 15-32 |

|          |                                                   |       |

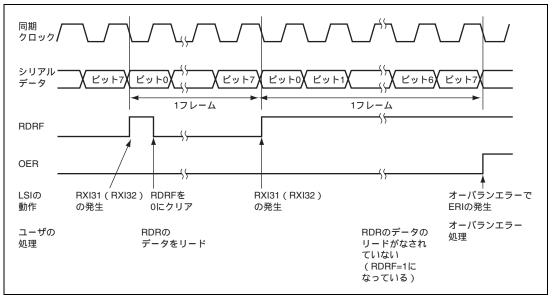

| 図 15.12   | クロック同期式モードの受信時の動作例                   | 15-33 |

|-----------|--------------------------------------|-------|

| 図 15.13   | データ受信フローチャートの例(クロック同期式モード)           | 15-34 |

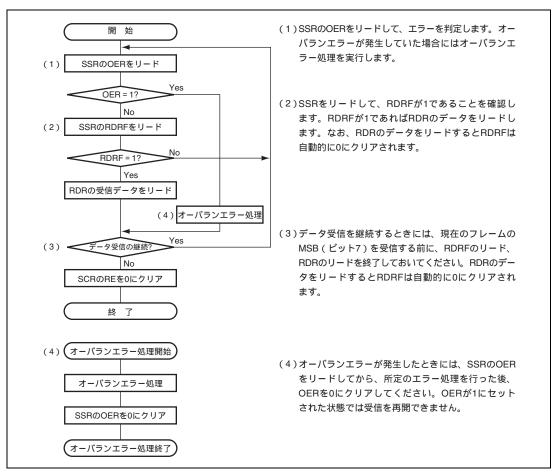

| 図 15.14   | データ送受信同時動作のフローチャートの例(クロック同期式モード)     | 15-35 |

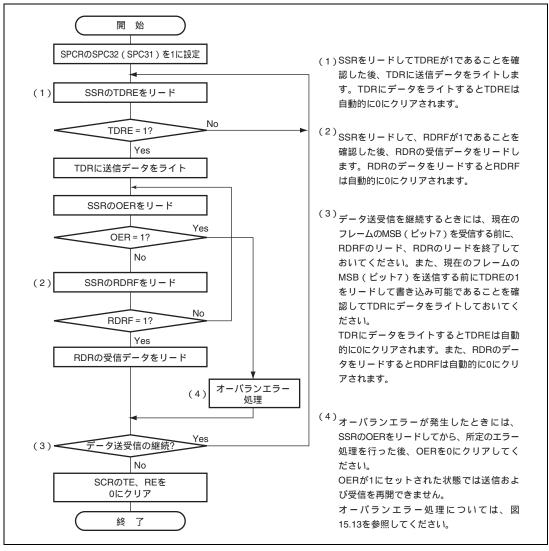

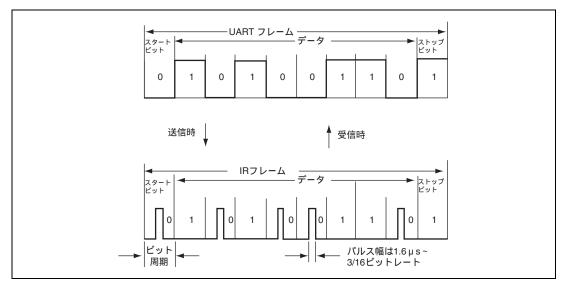

| 図 15.15   | IrDA プロック図                           | 15-36 |

| 図 15.16   | IrDA 送信 / 受信動作                       | 15-37 |

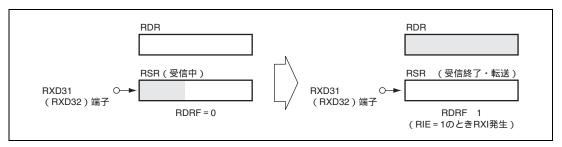

| 図 15.17 ( | (a) RDRFのセットと RXI 割り込み               | 15-41 |

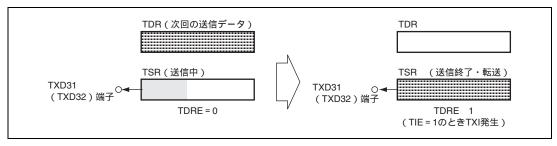

| 図 15.17 ( | ( b ) TDRE のセットと TXI 割り込み            | 15-41 |

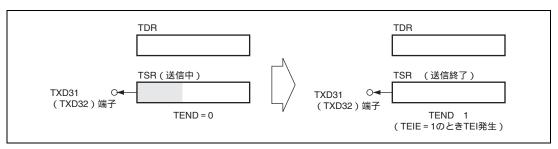

| 図 15.17 ( | ( c ) TEND のセットと TEI 割り込み            | 15-41 |

| 図 15.18   | 調歩同期式モードの受信データサンプリングタイミング            | 15-43 |

| 図 15.19   | RDR のリードタイミングとデータの関係                 | 15-44 |

| 16. シリア   | ルコミュニケーションインタフェース 4(SCI4)            | 16-1  |

| 図 16.1    | SCI4 のブロック図                          | 16-2  |

| 図 16.2    | 転送フォーマット                             | 16-8  |

| 図 16.3    | SCI4 を初期化するときのフローチャートの例              | 16-9  |

| 図 16.4    | データ送信のフローチャートの例                      | 16-10 |

| 図 16.5    | 送信時の動作例                              | 16-11 |

| 図 16.6    | データ受信フローチャートの例                       | 16-12 |

| 図 16.7    | 受信時の動作例                              | 16-13 |

| 図 16.8    | データ送受信同時動作のフローチャートの例                 | 16-14 |

| 図 16.9    | RDR4 リードタイミングとデータの関係                 | 16-17 |

| 図 16.10   | 内部クロック /2 選択時の転送フォーマット               | 16-17 |

| 17. 14ビッ  | y ► PWM                              | 17-1  |

| 図 17.1    | 14 ビット PWM のプロック図                    | 17-1  |

| 図 17.2    | 4 分割した場合のパルス分割方式 PWM の動作例            | 17-3  |

| ☒ 17.3    | PWM 出力波形                             | 17-4  |

| 18. A/D 変 | 換器                                   | 18-1  |

| 図 18.1    | A/D 変換器のブロック図                        | 18-2  |

| 図 18.2    | 外部トリガ入力タイミング                         | 18-6  |

| 図 18.3    | A/D 変換器の動作例                          | 18-7  |

| 図 18.4    | A/D 変換器の使用手順の概念フロー(ソフトウェアでポーリングする場合) | 18-8  |

| 図 18.5    | A/D 変換器の使用手順の概念フロー(割り込みを使用する場合)      | 18-8  |

| 図 18.6    | A/D 変換精度の定義(1)                       | 18-9  |

| 図 18.7    | A/D 変換精度の定義 (2)                      | 18-10 |

| 図 18.8    | アナログ入力回路の例                           | 18-11 |

| 19. LCD = | ıントローラ/ドライバ                          | 19-1  |

| 図 19.1    | LCD コントローラ / ドライバのブロック図              | 19-2  |

| 図 19.2                 | 1/2 デューティ時の LCD 駆動電源の処理             | 19-10 |

|------------------------|-------------------------------------|-------|

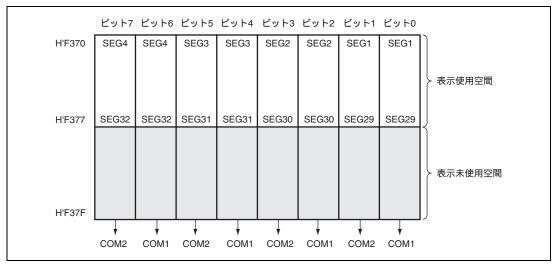

| 図 19.3                 | LCD RAM マップ(1/4 デューティ)              | 19-12 |

| 図 19.4                 | LCD RAM マップ ( 1/3 デューティ )           | 19-12 |

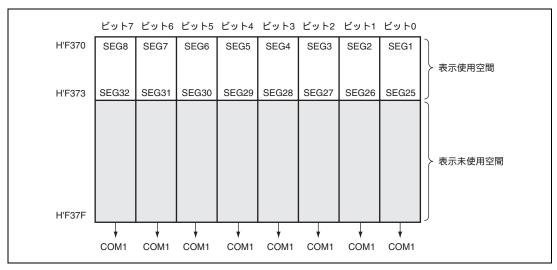

| 図 19.5                 | LCD RAM マップ(1/2 デューティ)              | 19-13 |

| 図 19.6                 | LCD RAM マップ(スタティック)                 | 19-13 |

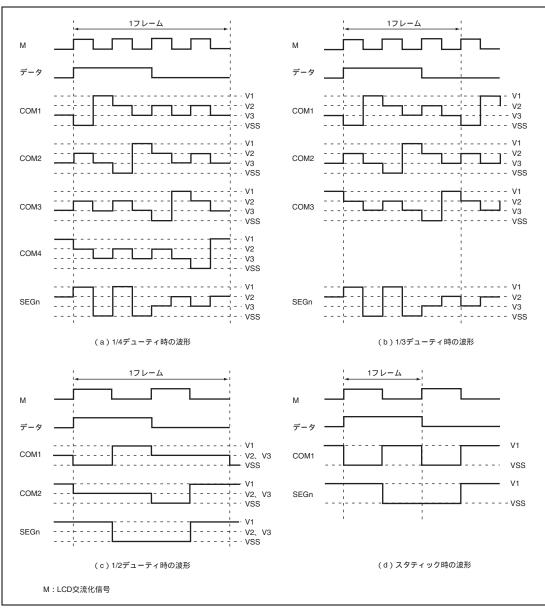

| 図 19.7                 | 各デューティでの出力波形(A 波形)                  | 19-14 |

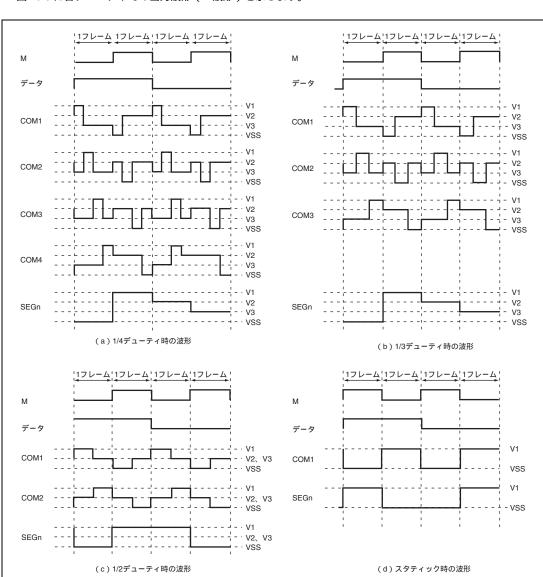

| 図 19.8                 | 各デューティでの出力波形(B 波形)                  | 19-15 |

| 図 19.9                 | 3V 定電圧電源回路使用時の接続方法                  | 19-17 |

| 図 19.10                | 外部分割抵抗の接続方法                         | 19-18 |

| 20. I <sup>2</sup> C バ | スインタフェース 2(IIC2)                    | 20-1  |

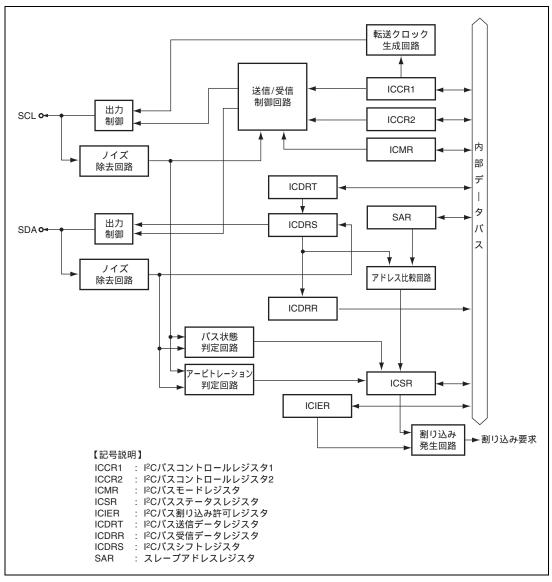

| ☑ 20.1                 | I <sup>2</sup> C バスインタフェース 2 のブロック図 | 20-2  |

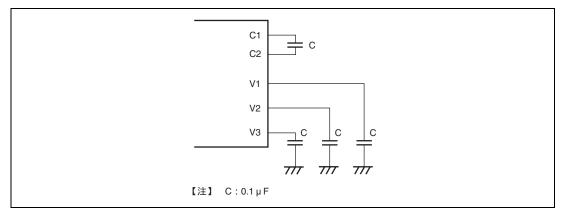

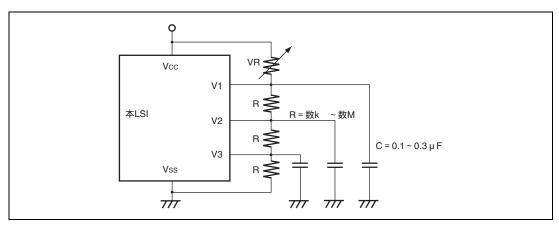

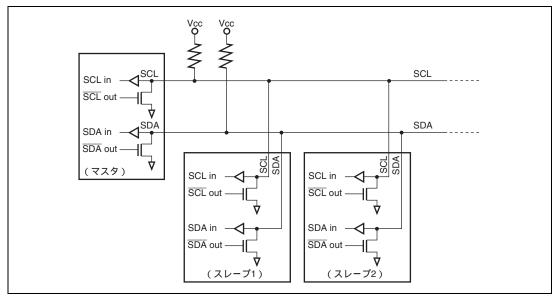

| 図 20.2                 | 入出力端子の外部回路接続例                       | 20-3  |

| 図 20.3                 | I <sup>2</sup> C バスフォーマット           | 20-13 |

| 図 20.4                 | I <sup>2</sup> C バスタイミング            | 20-13 |

| 図 20.5                 | マスタ送信モード動作タイミング(1)                  | 20-15 |

| 図 20.6                 | マスタ送信モード動作タイミング (2)                 | 20-15 |

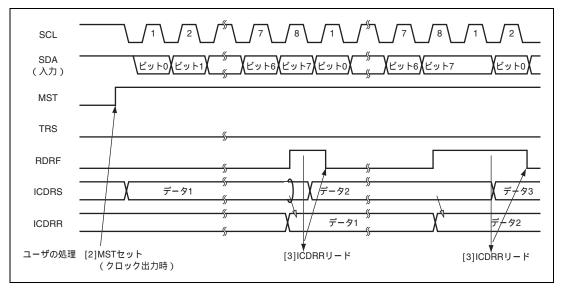

| 図 20.7                 | マスタ受信モード動作タイミング(1)                  | 20-17 |

| 図 20.8                 | マスタ受信モード動作タイミング (2)                 | 20-17 |

| 図 20.9                 | スレーブ送信モード動作タイミング (1)                | 20-19 |

| 図 20.10                | スレーブ送信モード動作タイミング(2)                 | 20-20 |

| 図 20.11                | スレープ受信モード動作タイミング (1)                | 20-21 |

| 図 20.12                | スレープ受信モード動作タイミング(2)                 | 20-21 |

| 図 20.13                | クロック同期式シリアルの転送フォーマット                | 20-22 |

| 図 20.14                | 送信モード動作タイミング                        | 20-23 |

| 図 20.15                | 受信モード動作タイミング                        | 20-24 |

| 図 20.16                | ノイズ除去回路のブロック図                       | 20-24 |

| 図 20.17                | マスタ送信モードのフローチャート例                   | 20-25 |

| 図 20.18                | マスタ受信モードのフローチャート例                   | 20-26 |

| 図 20.19                | スレーブ送信モードフローチャート例                   | 20-27 |

| 図 20.20                | スレープ受信モードフローチャート例                   | 20-28 |

| 図 20.21                | ビット同期回路のタイミング                       | 20-30 |

| 21. パワー                | - オンリセット回路                          | 21-1  |

| 図 21.1                 | パワーオンリセット回路                         | 21-1  |

| 図 21.2                 | パワーオンリセット回路動作タイミング                  | 21-2  |

| 22. アドレ                | ·スプレーク                              | 22-1  |

| 図 22.1                 | アドレスプレークプロック図                       | 22-1  |

| 図 22.2                 | アドレスブレーク割り込み動作例 (1)                 | 22-4  |

| 図 22.2    | アドレスブレーク割り込み動作例(2)                      | 22-5  |

|-----------|-----------------------------------------|-------|

| 24. 電気的   | 特性                                      | 24-1  |

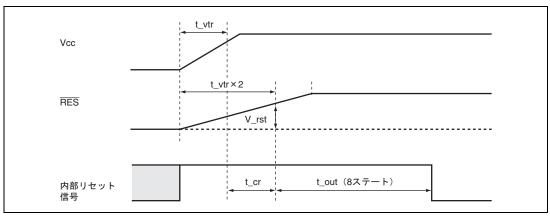

| ፟ 24.1    | パワーオンリセット回路リセットタイミング                    | 24-31 |

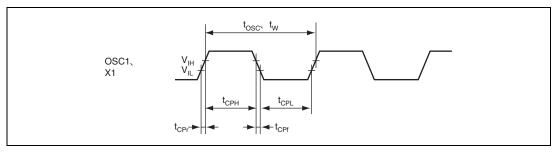

| ☑ 24.2    | クロック入力タイミング                             |       |

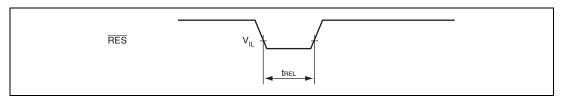

| ☑ 24.3    | RES 端子 Low レベル幅タイミング                    |       |

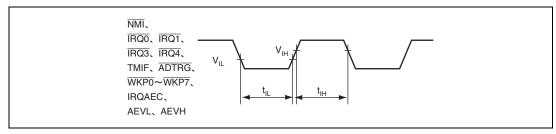

| ☑ 24.4    | 入力タイミング                                 |       |

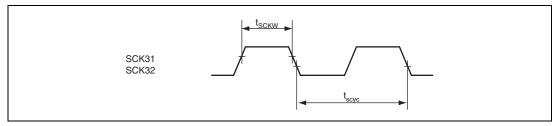

| 図 24.5    | SCK3 入力クロックタイミング                        | 24-32 |

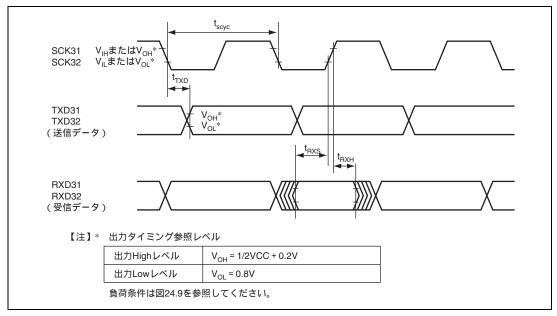

| 図 24.6    | SCI3 クロック同期式モード入出力タイミング                 | 24-33 |

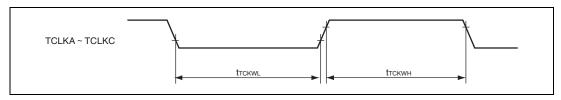

| 図 24.7    | TCLKA~TCLKC 端子クロック入力タイミング               | 24-33 |

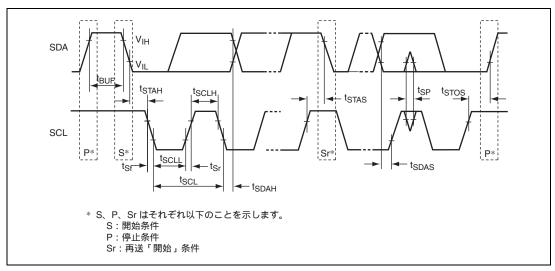

| 図 24.8    | I <sup>2</sup> C バスインタフェース入出力タイミング      | 24-33 |

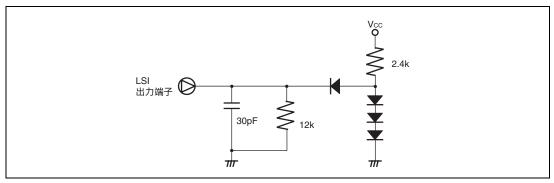

| 図 24.9    | 出力負荷条件                                  | 24-34 |

| 付録        |                                         | 付録-1  |

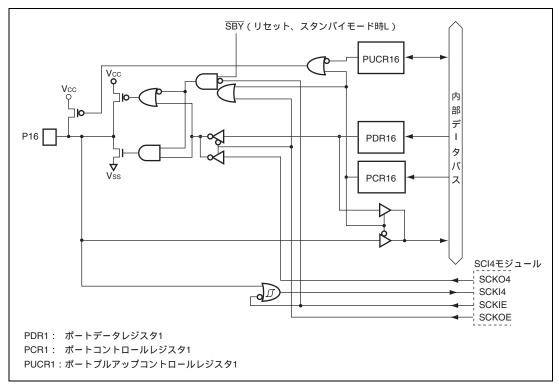

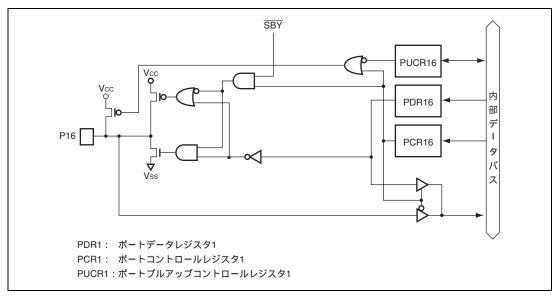

| 図 B.1 (a  | ı) ポート 1 ブロック図(P16 端子)(F-ZTAT 版)        | 付録-29 |

| 図 B.1 ( b | o) ポート 1 ブロック図(P16 端子)(マスク ROM 版)       | 付録-30 |

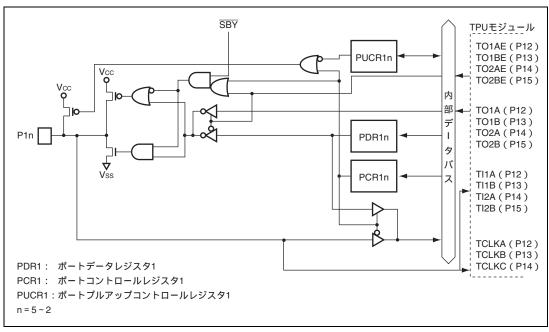

| 図 B.1 ( c | ; ) ポート 1 ブロック図(P15~P12 端子)             | 付録-30 |

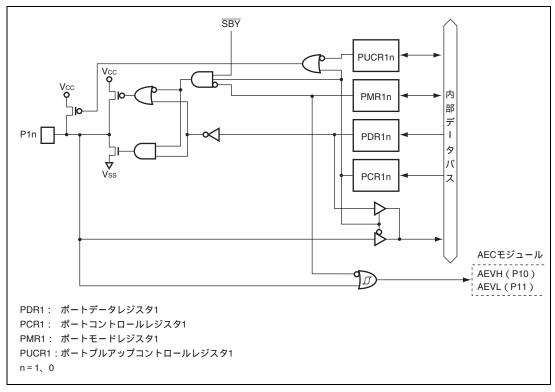

| 図 B.1 ( d | l) ポート 1 ブロック図(P11、P10 端子)              | 付録-31 |

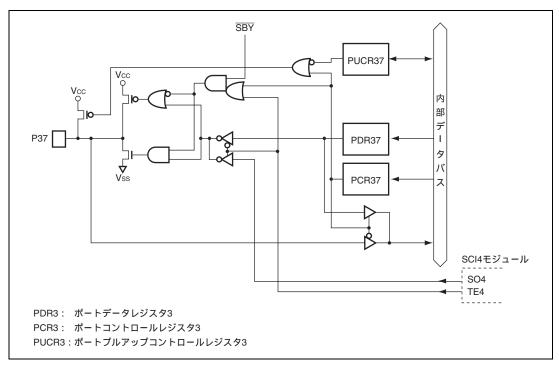

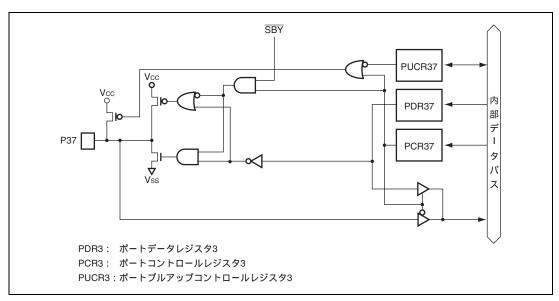

| 図 B.2 (a  | ı) ポート 3 ブロック図(P37 端子)(F-ZTAT 版)        | 付録-32 |

| 図 B.2 ( t | o) ポート 3 ブロック図(P37 端子)(マスク ROM 版)       | 付録-32 |

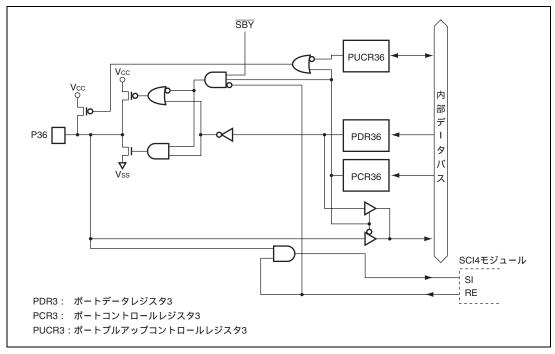

| 図 B.2(c   | :) ポート 3 ブロック図(P36 端子)(F-ZTAT 版)        | 付録-33 |

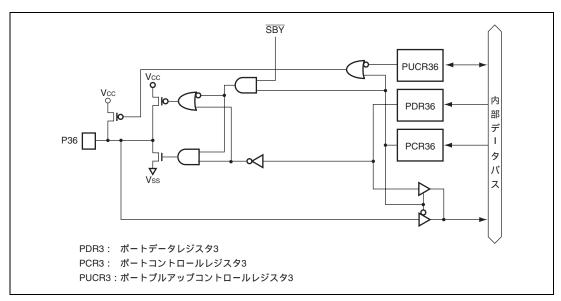

| 図 B.2(d   | 1) ポート 3 ブロック図(P36 端子)(マスク ROM 版)       | 付録-33 |

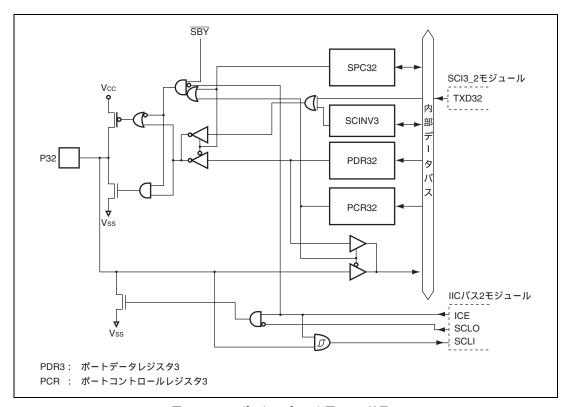

| 図 B.2 ( e | e) ポート 3 ブロック図 ( P32 端子 )               | 付録-34 |

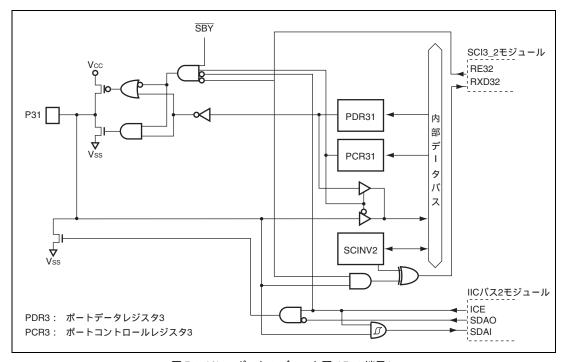

| 図 B.2 (f  | ) ポート 3 ブロック図(P31 端子)                   | 付録-35 |

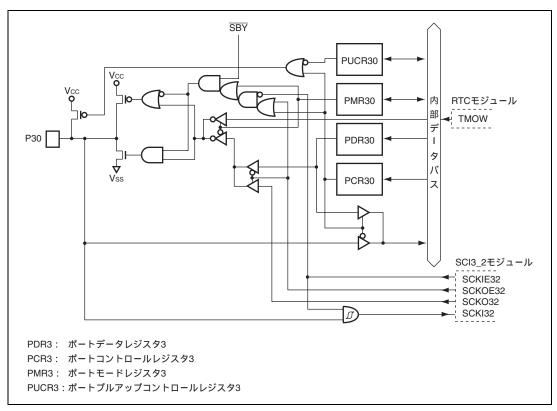

| 図 B.2(g   | g) ポート 3 ブロック図(P30 端子)                  | 付録-36 |

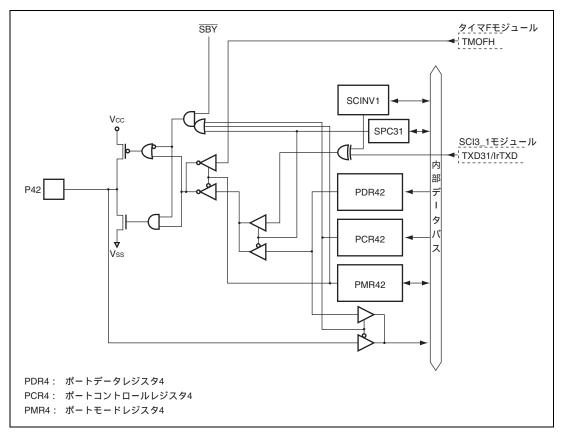

| 図 B.3 (a  | ı) ポート 4 ブロック図(P42 端子)                  | 付録-37 |

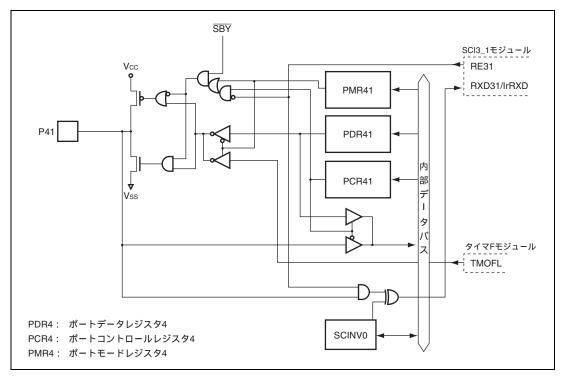

| 図 B.3 ( t | o) ポート 4 ブロック図(P41 端子)                  | 付録-38 |

| 図 B.3 ( c | · ) ポート 4 ブロック図(P40 端子)                 | 付録-39 |

| 図 B.4     | ポート 5 ブロック図                             | 付録-40 |

| 図 B.5     | ポート 6 ブロック図                             | 付録-40 |

| 図 B.6     | ポート 7 ブロック図                             | 付録-41 |

| 図 B.7     | ポート 8 ブロック図                             | 付録-41 |

| 図 B.8 (a  | a) ポート 9 ブロック図(P93 端子)                  | 付録-42 |

| 図 B.8(t   | o) ポート 9 ブロック図(P92 端子)                  | 付録-42 |

| 図 B.8 ( c | e) ポート 9 ブロック図(P91、P90 端子)              | 付録-43 |

| 図 B.9     | ポート A ブロック図                             |       |

| 図 B.10 (  | , , , , , , , , , , , , , , , , , , , , |       |

| 図 B.10 (  |                                         |       |

| 図 D.1     | 外形寸法図(FP-80A)                           | 付録-48 |

| 図 D.2     | 外形寸法図 ( TFP-80C )                       | 付録-49 |

| 図 D.3 | 外形寸法図(TLP-85V)                                                        | 付録-50              |

|-------|-----------------------------------------------------------------------|--------------------|

| 図 E.1 | チップ断面図 (HCD64338076R、HCD64338075R、HCD64338074R、HCD                    | D64338073R)付録-51   |

| 図 E.2 | チップ断面図 (HCD64F38076R)                                                 | 付録-51              |

| 図 F.1 | ボンディングパッド形状図<br>(HCD64F38076R、HCD64338076R、HCD64338075R、HCD64338074R、 | HCD64338073R)付録-52 |

| 図 G.1 | チップトレイ仕様図<br>(HCD64F38076R、HCD64338076R、HCD64338075R、HCD64338074R、    | HCD64338073R)付録-53 |

| 図 G.2 | チップトレイ仕様図 ( HCD64F38076R )                                            | 付録-54              |

## 表目次

| 1. | 概要…    |                             | 1-1  |

|----|--------|-----------------------------|------|

|    | 表 1.1  | TLP-85V ピン配置対応              | 1-6  |

|    | 表 1.2  | パッド座標                       | 1-10 |

|    | 表 1.3  | パッド座標                       | 1-14 |

|    | 表 1.4  | 端子機能                        | 1-17 |

| 2. | CPU    |                             | 2-1  |

|    | 表 2.1  | オペレーションの記号                  | 2-9  |

|    | 表 2.2  | データ転送命令                     | 2-10 |

|    | 表 2.3  | 算術演算命令                      | 2-10 |

|    | 表 2.4  | 論理演算命令                      | 2-12 |

|    | 表 2.5  | シフト命令                       | 2-12 |

|    | 表 2.6  | ビット操作命令                     | 2-13 |

|    | 表 2.7  | 分岐命令                        | 2-15 |

|    | 表 2.8  | システム制御命令                    | 2-16 |

|    | 表 2.9  | ブロック転送命令                    | 2-16 |

|    | 表 2.10 | アドレッシングモードー覧表               | 2-18 |

|    | 表 2.11 | 絶対アドレスのアクセス範囲               | 2-19 |

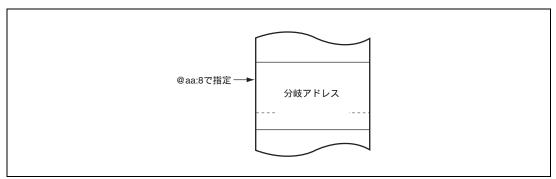

|    | 表 2.12 | 実効アドレスの計算方法 (1)             | 2-21 |

|    | 表 2.12 | 実効アドレスの計算方法 (2)             | 2-22 |

| 3. | 例外処    | 理                           | 3-1  |

|    | 表 3.1  | 例外処理要因とベクタアドレス              | 3-2  |

|    | 表 3.2  | リセット要因                      | 3-3  |

|    | 表 3.3  | 割り込み要求待ちステート数               | 3-6  |

|    | 表 3.4  | 割り込み要求フラグが 1 にセットされる条件      | 3-8  |

| 4. | 割り込    | みコントローラ                     | 4-1  |

|    | 表 4.1  | 端子構成                        | 4-2  |

|    | 表 4.2  | 割り込み要因とベクタアドレスおよび割り込み優先順位一覧 | 4-13 |

|    | 表 4.3  | 割り込み制御状態                    | 4-15 |

|    | 表 4.4  | 割り込み応答時間                    | 4-18 |

| 5. クロッ  | ック発振器                        | 5-1   |

|---------|------------------------------|-------|

| 表 5.1   | システムクロック発振器と内蔵発振器の選択方法       | 5-5   |

| 6. 低消費  | <b>貴電力モード</b>                | 6-1   |

| 表 6.1   | 動作周波数と待機時間                   | 6-3   |

| 表 6.2   | SLEEP 命令実行後の状態と割り込みによる復帰先    |       |

| 表 6.3   | 各動作モードでの LSI の状態             |       |

| 7. ROM  |                              | 7-1   |

| 表 7.1   | プログラミングモード選択方法               | 7-6   |

| 表 7.2   | ブートモードの動作                    |       |

| 表 7.3   | ビットレート自動合わせ込みが可能なシステムクロック周波数 |       |

| 表 7.4   | 再書き込みデータ演算表                  |       |

| 表 7.5   |                              |       |

| 表 7.6   | 書き込み時間                       | 7-12  |

| 表 7.7   | フラッシュメモリの動作状態                | 7-16  |

| 10. リアノ | レタイムクロック(RTC)                | 10-1  |

| 表 10.1  | 端子構成                         | 10-2  |

| 表 10.2  | 割り込み要因                       | 10-10 |

| 11. タイマ | ζ F                          | 11-1  |

| 表 11.1  | 端子構成                         | 11-2  |

| 表 11.2  | タイマFの動作モード                   | 11-10 |

| 12. 16ビ | ットタイマパルスユニット(TPU)            | 12-1  |

| 表 12.1  | TPU の機能一覧                    | 12-2  |

| 表 12.2  | 端子構成                         | 12-3  |

| 表 12.3  | CCLR1 ~ CCLR0 (チャネル1、2)      | 12-5  |

| 表 12.4  | TPSC2~TPSC0 (チャネル1)          | 12-6  |

| 表 12.5  | TPSC2~TPSC0 (チャネル2)          | 12-6  |

| 表 12.6  | MD3 ~ MD0                    | 12-7  |

| 表 12.7  | TIOR_1 (チャネル1)               | 12-8  |

| 表 12.8  | TIOR_2 (チャネル2)               | 12-8  |

| 表 12.9  | TIOR_1 (チャネル1)               | 12-9  |

| 表 12.10 | TIOR_2 (チャネル 2)              | 12-10 |

| 表 12.11 | カスケード接続組み合わせ                 | 12-22 |

| 表 12.12 | 各 PWM 出力のレジスタと出力端子           | 12-24 |

| 表 12.13 | TPU 割り込み一覧                   | 12-28 |

| 13. 非同期   | イベントカウンタ(AEC)                         | 13-1  |

|-----------|---------------------------------------|-------|

| 表 13.1    | 端子構成                                  | 13-2  |

| 表 13.2    | イベントカウンタ PWM 動作例                      | 13-11 |

| 表 13.3    | 非同期イベントカウンタの動作モード                     | 13-12 |

| 表 13.4    | 最大クロック周波数                             | 13-13 |

| 15. シリア   | 'ルコミュニケーションインタフェース 3(SCI3、IrDA)       | 15-1  |

| 表 15.1    | SCI3 のチャネル構成                          | 15-2  |

| 表 15.2    | 端子構成                                  | 15-5  |

| 表 15.3    | ビットレートに対する BRR の設定例〔調歩同期式モード〕 ( 1 )   | 15-13 |

| 表 15.3    | ビットレートに対する BRR の設定例〔調歩同期式モード〕 ( 2 )   | 15-13 |

| 表 15.3    | ビットレートに対する BRR の設定例〔調歩同期式モード〕(3)      | 15-14 |

| 表 15.3    | ビットレートに対する BRR の設定例〔調歩同期式モード〕 (4)     | 15-14 |

| 表 15.3    | ビットレートに対する BRR の設定例〔調歩同期式モード〕(5)      | 15-15 |

| 表 15.4    | n とクロックの関係                            | 15-15 |

| 表 15.5    | 各周波数における最大ビットレート〔調歩同期式モード〕            | 15-16 |

| 表 15.6    | ビットレートに対する BRR の設定例〔クロック同期式モード〕 ( 1 ) | 15-17 |

| 表 15.6    | ビットレートに対する BRR の設定例〔クロック同期式モード〕 (2)   | 15-17 |

| 表 15.7    | n とクロックの関係                            | 15-18 |

| 表 15.8    | 通信フォーマット(調歩同期式モード)                    | 15-22 |

| 表 15.9    | SMR の設定値と送信 / 受信フォーマット                | 15-23 |

| 表 15.10   | SMR、SCR の設定とクロックソースの選択                | 15-23 |

| 表 15.11   | SSR のステータスフラグの状態と受信データの転送             | 15-28 |

| 表 15.12   | IrCKS2~IrCKS0 ビットの設定                  | 15-38 |

| 表 15.13   | SCI3 の割り込み要求                          | 15-39 |

| 表 15.14   | 送信 / 受信割り込み                           | 15-40 |

| 16. シリア   | 'ルコミュニケーションインタフェース 4(SCl4)            | 16-1  |

| 表 16.1    | 端子構成                                  | 16-2  |

| 表 16.2    | プリスケーラ分周比と転送クロック周期(内部クロックの場合)         | 16-7  |

| 表 16.3    | SCI4 割り込み要求の内容                        | 16-15 |

| 17. 14ビ   | y ト PWM                               | 17-1  |

| 表 17.1    | 端子構成                                  | 17-2  |

| 表 17.2    | PWCR、PWDR と出力波形の関係                    | 17-4  |

| 表 17.3    | PWM の動作モード                            | 17-5  |

| 18. A/D 変 | 換器                                    | 18-1  |

| 表 18.1    | 端子構成                                  | 18-3  |

| 表 18.2    | A/D 変換器の動作モード                         | 18-6  |

| 19. LCD                | コントローラ / ドライバ                   | 19-1  |

|------------------------|---------------------------------|-------|

| 表 19.1                 | 端子構成                            | 19-3  |

| 表 19.2                 | デューティ比、コモン機能の選択                 | 19-4  |

| 表 19.3                 | セグメントドライバの選択                    | 19-5  |

| 表 19.4                 | フレーム周波数の選択                      | 19-6  |

| 表 19.5                 | 出力レベルの関係                        | 19-16 |

| 表 19.6                 | 低消費電力モードと表示動作の関係                | 19-17 |

| 20. I <sup>2</sup> C バ | スインタフェース 2 ( IIC2 )             | 20-1  |

| 表 20.1                 | 端子構成                            | 20-3  |

| 表 20.2                 | 転送レート                           | 20-5  |

| 表 20.3                 | 割り込み要求一覧                        | 20-29 |

| 表 20.4                 | SCL をモニタする時間                    | 20-30 |

| 22. アドレ                | ·スプレーク                          | 22-1  |

| 表 22.1                 | 使用するデータバス                       | 22-3  |

| 表 22.2                 | アドレスブレークの動作モード                  | 22-5  |

| 24. 電気的                | 9特性                             | 24-1  |

| 表 24.1                 | 絶対最大定格                          | 24-1  |

| 表 24.2                 | DC 特性                           | 24-5  |

| 表 24.3                 | 制御信号タイミング                       | 24-10 |

| 表 24.4                 | シリアルインタフェースタイミング                | 24-12 |

| 表 24.5                 | I <sup>2</sup> C バスインタフェースタイミング | 24-12 |

| 表 24.6                 | A/D 变換器特性                       | 24-13 |

| 表 24.7                 | LCD 特性                          | 24-14 |

| 表 24.8                 | パワーオンリセット回路特性                   | 24-14 |

| 表 24.9                 | ウォッチドッグタイマ特性                    | 24-15 |

| 表 24.10                | フラッシュメモリ特性                      | 24-15 |

| 表 24.11                | 絶対最大定格                          | 24-17 |

| 表 24.12                | DC 特性                           | 24-21 |

| 表 24.13                | 制御信号タイミング                       | 24-26 |

| 表 24.14                | シリアルインタフェースタイミング                | 24-28 |

| 表 24.15                | I <sup>2</sup> C バスインタフェースタイミング | 24-28 |

| 表 24.16                | A/D 変換器特性                       | 24-29 |

| 表 24.17                | LCD 特性                          | 24-30 |

| 表 24.18                | パワーオンリセット回路特性                   | 24-31 |

| 表 24.19                | ウォッチドッグタイマ特性                    | 24-31 |

| 付録    |                         | 付録-1  |

|-------|-------------------------|-------|

| 表 A.1 | 命令セット一覧                 | .付録-3 |

| 表 A.2 | オペレーションコードマップ(1)1       | 付録-16 |

| 表 A.2 | オペレーションコードマップ(2)        | 付録-17 |

| 表 A.2 | オペレーションコードマップ(3)        | 付録-18 |

| 表 A.3 | 実行状態 ( サイクル ) に要するステート数 | 付録-19 |

| 表 A.4 | 命令の実行状態(サイクル数)          | 付録-20 |

| 表 A.5 | 命令とアドレッシングモードの組み合わせ     | 付録-28 |

|       |                         |       |

# 1. 概要

# 1.1 特長

• 16ビット高速H8/300H CPU

H8/300 CPUとオブジェクトレベルで上位互換

汎用レジスタ:16ビット×16本

基本命令:62種類

• 豊富な周辺機能

RTC (フリーランカウンタとしても使用可能)

非同期イベントカウンタ(AEC)

LCDコントローラ / ドライバ

タイマF

16ビットタイマパルスユニット (TPU)

14ビットPWM

ウォッチドッグタイマ

SCI (調歩同期式またはクロック同期式シリアルコミュニケーションインタフェース)

I<sup>2</sup>Cバスインタフェース(フィリップス社が提唱するI<sup>2</sup>Cバスインタフェース方式に準拠)

10ビットA/D変換器

#### 内蔵メモリ

| 製品分類                             |            | 製品型名        | ROM      | RAM    |

|----------------------------------|------------|-------------|----------|--------|

| フラッシュメモリ版(F-ZTAT <sup>™</sup> 版) | H8/38076RF | HD64F38076R | 52k バイト* | 3k バイト |

| マスク ROM 版                        | H8/38076R  | HD64338076R | 48k バイト  | 2k バイト |

|                                  | H8/38075R  | HD64338075R | 40k バイト  | 2k バイト |

|                                  | H8/38074R  | HD64338074R | 32k バイト  | 1k バイト |

|                                  | H8/38073R  | HD64338073R | 24k バイト  | 1k バイト |

- 【注】 F-ZTAT<sup>™</sup>は(株)ルネサス テクノロジの商標です。

- \* 52k バイトのうち 4k バイトはオンチップデバッギングエミュレータで使用します。オンチップデバッギングエミュレータを使用しない場合は 52k バイト有効です。

- 汎用入出力ポート

入出力ポート: 55本。このうち大電流ポート4本 (IoL = 15mA @VoL = 1.0V)

入力ポート:8本

- 各種低消費電力モードをサポート

- 小型パッケージ

| パッケージ      | コード          | 旧コード    | ボディサイズ    | ピンピッチ  | 備考 |

|------------|--------------|---------|-----------|--------|----|

| QFP-80     | PRQP0080JB-A | FP-80A  | 14 × 14mm | 0.65mm |    |

| TQFP-80    | PTQP0080KC-A | TFP-80C | 12 × 12mm | 0.5mm  |    |

| P-TFLGA-85 | PTLG0085JA-A | TLP-85V | 7 × 7mm   | 0.65mm |    |

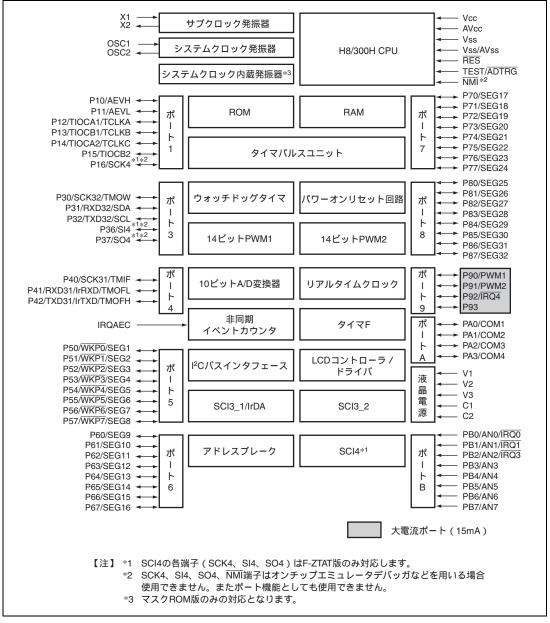

# 1.2 内部ブロック図

図 1.1 H8/38076R グループ内部ブロック図

### 1.3 ピン配置図

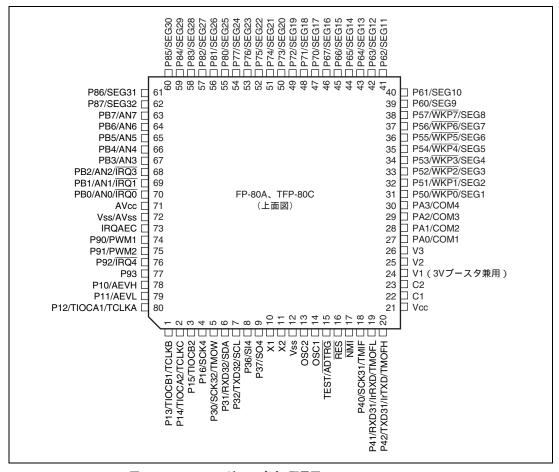

図 1.2 H8/38076R グループピン配置図 (FP-80A、TFP-80C)

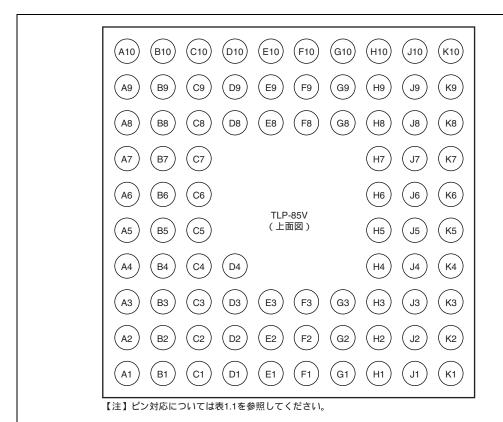

図 1.3 H8/38076R グループピン配置図 (TLP-85V)

表 1.1 TLP-85V ピン配置対応

| HB/38076R グループ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 端子名                   | ピン記号        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-------------|

| P14/TIOCA2/TCLKC         C1           P15/TIOCB2         B2           P16/SCK4         C2           P30/SCK32/TMOW         D1           P31/RXD32/SDA         D3           P32/TXD32/SCL         D2           P36/SI4         E1           P37/SO4         E3           X1         F2           X2         E2           Vss         F3           OSC2         G3           OSC1         F1           TEST/ADTRG         G2           RES         H2           NMI         G1           P40/SCK31/TMIF         H3           P41/RXD31/IRXD/TMOFL         J1           P42/TXD31/IRXD/TMOFL         H1           NC         K1           Vc         K2           C1         K3           C2         J2           V1         J3           V2         K4           V3         H4           PAI/COM1         J4           PAI/COM2         K5           PA2/COM3         H5           PA3/COM4         J6           P50/WKP0/SeG1         J6           P50/WKP2/SeG3                                  | H8/38076R グループ        | ( TLP-85V ) |

| P16/SCK4         C2           P30/SCK32/TMOW         D1           P31/RXD32/SDA         D3           P32/TXD32/SCL         D2           P36/SI4         E1           P37/SO4         E3           X1         F2           X2         E2           Vss         F3           OSC2         G3           OSC1         F1           TEST/ADTRG         G2           RES         H2           NMI         G1           P40/SCK31/TMIF         H3           P41/RXD31/IRXD/TMOFL         J1           P42/TXD31/ITXD/TMOFH         H1           NC         K2           C1         K3           C2         J2           V1         K3           C2         J2           V1         K4           V3         K4           V3         K4           V4         J3           V2         K4           V3         K4           V4         J4           V3         K4           V4         J4           V5         K5           P60/CMQ1                                                                        | P13/TIOCB1/TCLKB      | B1          |

| P16/SCK4         C2           P30/SCK32/TMOW         D1           P31/RXD32/SDA         D3           P32/TXD32/SCL         D2           P36/S14         E1           P37/SO4         E3           X1         F2           X2         E2           Vss         F3           OSC2         G3           OSC1         F1           TEST/ADTRG         G2           RES         H2           NMI         G1           P40/SCK31/TMIF         H3           P41/RXD31/IrRXD/TMOFL         J1           P42/TXD31/IrXD/TMOFH         H1           NC         K2           C1         K3           C2         J2           V1         K3           C2         J2           V1         K4           V3         K4           V3         K4           V3         H4           PAI/COM1         J4           PAI/COM2         K5           PAI/COM3         H5           PAI/COM4         J6           PS0/WKP0/SEG1         J6           PS0/WKP0/SEG3         H6 </td <td>P14/TIOCA2/TCLKC</td> <td>C1</td> | P14/TIOCA2/TCLKC      | C1          |

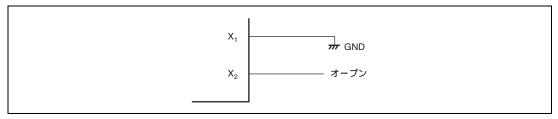

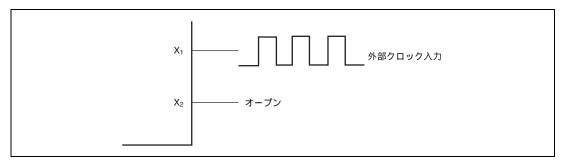

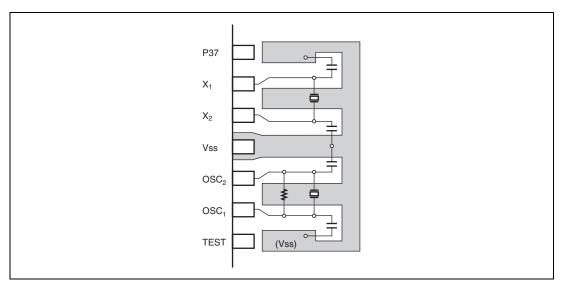

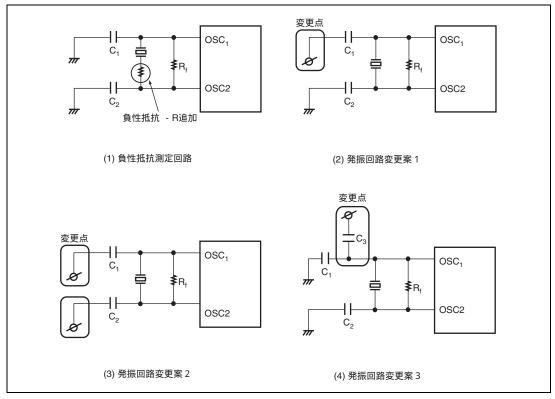

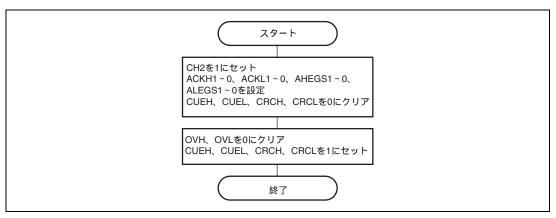

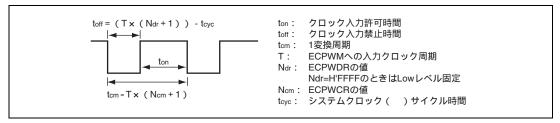

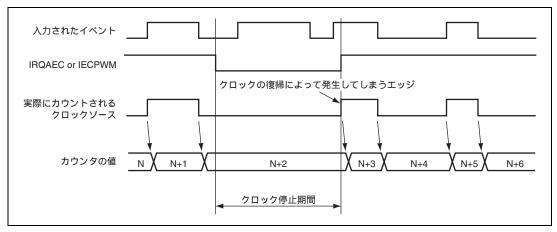

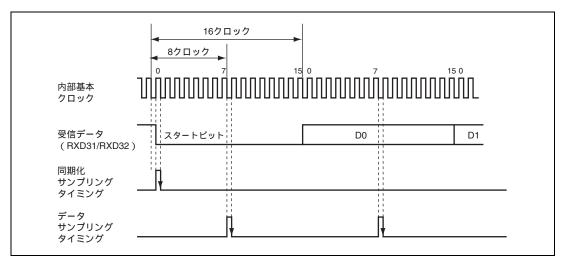

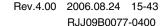

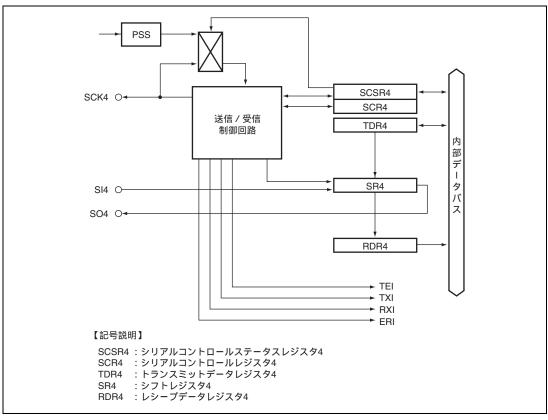

| P30/SCK32/TMOW         D1           P31/RXD32/SDA         D3           P32/TXD32/SCL         D2           P36/SI4         E1           P37/SO4         E3           X1         F2           X2         E2           Vss         F3           OSC2         G3           OSC1         F1           TEST/ADTRG         G2           RES         H2           NMI         G1           P40/SCK31/TMIF         H3           P41/RXD31/IrRXD/TMOFL         J1           P42/TXD31/IrTXD/TMOFH         H1           NC         K2           C1         K3           C2         J2           V1         J3           V2         K4           V3         H4           V3         H4           V3         H4           PA0/COM1         J4           PA1/COM2         K5           PA2/COM3         H5           P50/WKP0/SEG1         J5           P50/WKP0/SEG3         H6                                                                                                                               | P15/TIOCB2            | B2          |